# Module 1

# Introduction

The first integrated circuit was flip-flop with two transistors built by Jack Kilby at Texas Instruments in the year 1958. In the year 2008, Intel's Itanium microprocessor contained more than 2 billion transistors and a 16 Gb Flash memory contained more than 4 billion transistors. So in the range of over 50 years there is the growth rate is around 53%. This incredible growth has come from steady miniaturization of transistors and improvements in manufacturing processes. As transistors became smaller, they also became faster, dissipate less power, and are got cheaper to manufacture. The memory once needed for an entire company's accounting system is now carried by a teenager in her iPod. Improvements in integrated circuits have enabled space exploration, made automobiles safer and more fuel efficient, revolutionized the nature of warfare, brought much of mankind's knowledge to our Web browsers, and made the world a flatter place.

- During the first half of the twentieth century, electronic circuits used large, expensive, power-hungry, and unreliable vacuum tubes.

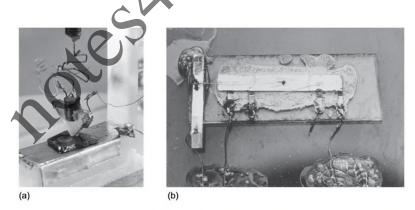

- In 1947, John Bardeen and Walter Brattain built the first functioning point contact transistor at Bell Laboratories, shown in Figure 1.1(a).

- Later it was introduced by the Bell Lab and named it as **Transistor, T-R-A-N-S-I-S-T-O-R**, because it is a resistor or semiconductor device which can amplify electrical signals as they are transferred through it from input to output terminals.

- Ten years later, Jack Kilby at Texas Instruments realized the potential for miniaturization if multiple transistors could be built on one piece of silicon. Figure 1.1(b) shows his first prototype of an integrated circuit, constructed from a germanium slice and gold wires.

Fig. 1.1(a) First transistor (b) First Integrated Circuit

- Transistors are electrically controlled switches with a control terminal and two other terminals that are connected or disconnected depending on the voltage or current applied to the control.

- After the invention of point contact transistor, Bell Labs developed the bipolar junction transistor, which were more reliable, less noisy and more power-efficient.

- Early integrated circuits used mainly bipolar transistors, which required a small current into the control (base) terminal to switch much larger currents between the other two (emitter and collector) terminals.

- The problem seen with bipolar transistors were the power dissipated by the base current which limited the maximum number of transistors that can be integrated onto a single die.

- Then in 1960 came Metal Oxide Semiconductor Field Effect Transistors (MOSFETs). The advantages seen in MOSFETs were that they draw almost zero control current while idle. It was available in 2 forms as: nMOS and pMOS, using n-type and p-type silicon, respectively.

- In 1963, the first logic gates using MOSFETs was introduced at Fairchild. It included gates used both nMOS and pMOS transistors. This gave the name Complementary Metal Oxide Semiconductor, or CMOS. The circuits used discrete transistors but consumed only nanowatts of power, which was about six times lesser than bipolar transistors.

- MOS ICs became popular because of their low cost, each transistor occupied less area and the fabrication process was simpler. Early commercial processes used only pMOS transistors but it suffered from poor performance, yield, and reliability. Later on Processes using nMOS transistors became common in the 1970s.

- Even though nMOS process was less expensive compared to CMOS, nMOS logic gates consumed power while they were idle. Power consumption became a major issue in the 1980s as hundreds of thousands of transistors were integrated onto a single die. CMOS processes were widely adopted and have essentially replaced nMOS and bipolar processes for nearly all digital logic applications.

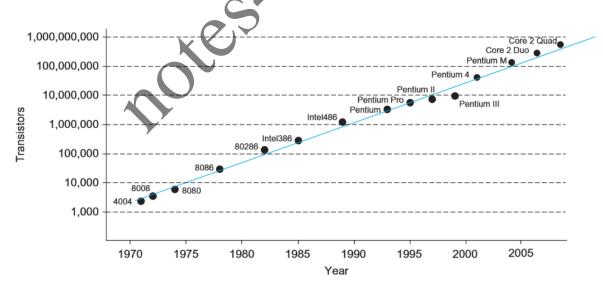

- In 1965, Gordon Moore observed that plotting the number of transistors that can be most economically manufactured on a chip gives a straight line on a semi-logarithmic scale. Also he found transistor count doubling every 18 months. This observation has been called **Moore's Law**.

- Fig 1.2 shows that the number of transistors in Intel microprocessors has doubled every 26 months since the invention of the 4004.

- Moore's Law is based on scaling down the size of transistors and to some extent building larger chips.

Fig 1.2 Transistors in Intel microprocessors

## Level of Integration:

The process of integration can be classified as small, medium, large, very large.

1. Small-Scale Integration (SSI): The number of components is less than 10 in every package. Logic Gates like inverters, AND gate, OR gate and etc. are products of SSI.

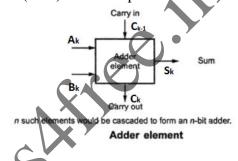

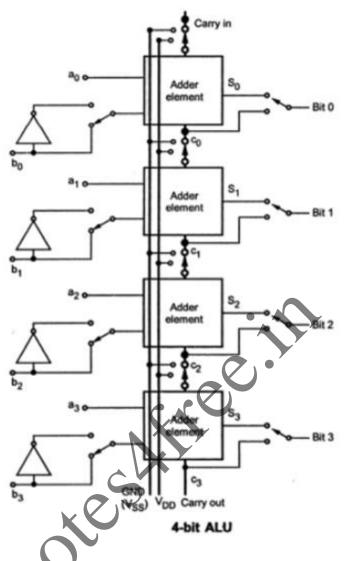

- 2. Medium Scale Integration (MSI): MSI devices has a complexity of 10 to 100 electronic components in a single package. Ex: decoders, adders, counters, multiplexers, and demultiplexers.

- 3. Large Scale Integration (LSI): Products of LSI contain between 100 and 10,000 electronic components in a single package. Ex: memory modules, I/O controllers, and 4-bit microprocessor systems.

- 4. Very Large Scale Integration (VLSI): Devices that are results of VLSI contain between 10,000 and 300,000 electronic components. Ex: 8bit, 16-bit, and 32-bit microprocessor systems.

- The feature size of a CMOS manufacturing process refers to the minimum dimension of a transistor that can be reliably built. The 4004 had a feature size of  $10\mu$  m in 1971. The Core 2 Duo had a feature size of 45nm in 2008. Feature sizes specified in microns ( $10^{-6}$ m), while smaller feature sizes are expressed in nanometers ( $10^{-9}$  m).

## **MOS Transistor:**

- Silicon (Si), a semiconductor, forms the basic starting material for most integrated circuits

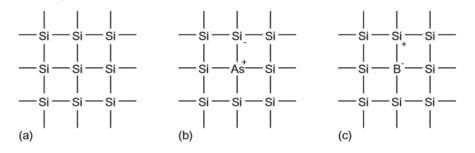

- Silicon is a Group IV element in periodic table, it forms covalent bonds with four adjacent atoms, as shown in Figure 1.3(a). As the valence electrons of it are involved in chemical bonds, pure silicon is a poor conductor.

- However its conductivity can be increased by introducing small amounts of impurities, called dopants, into the silicon lattice.

- A dopant from Group V of the periodic table, such as arsenic, having five valence electrons. It replaces a silicon atom in the lattice and still bonds to four neighbors, so the fifth valence electron is loosely bound to the arsenic atom, as shown in Figure 1.3(b). Thermal vibration at room temperature is sufficient to free the electron. This results in As+ ion and a free electron. The free electron can carry current and this is an n-type semiconductor.

Fig 1.3 Silicon lattice and dopant atoms

- A Group III dopant, such as boron, having three valence electrons, as shown in Fig 1.3(c). The dopant atom can borrow an electron from a neighboring silicon atom, which in turn becomes short by one electron. That atom in turn can borrow an electron, and so forth, so the missing electron, or hole, can propagate about the lattice. The hole acts as a positive carrier so we call this a p-type semiconductor.

- A Metal-Oxide-Semiconductor (MOS) structure is created by superimposing several layers of conducting and insulating materials to form a sandwich-like structure.

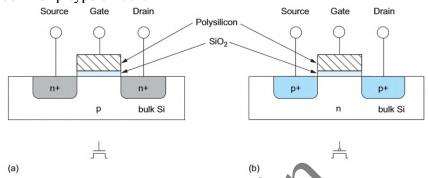

- Transistors can be built on a single crystal of silicon, which are available as thin flat circular wafer of 15–30 cm in diameter. CMOS technology provides two types of transistors an n-type transistor (nMOS) and a p-type transistor (pMOS).

- Transistor operation is controlled by electric fields so the devices are also called Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) or simply FETs. Cross-sections and symbols of these transistors are shown in Figure 1.4. The n+ and p+ regions indicate heavily doped n- or p-type silicon.

Fig 1.4 (a) nMOS transistor and (b) pMOS transistor

- Each transistor has conducting gate, an insulating layer of silicon dioxide (SiO2, also known as glass), and the silicon wafer, also called the substrate/body/bulk. Gates of early transistors were built from metal, so was called Metal-Oxide-Semiconductor, or MOS.

- Even though the gate has been formed from polycrystalline silicon (polysilicon), the name is still metal.

- An nMOS transistor is built with a p-type body and has regions of n-type semiconductor adjacent to the gate called the source and drain. They are physically equivalent and they can be interchangeable. The body is typically grounded.

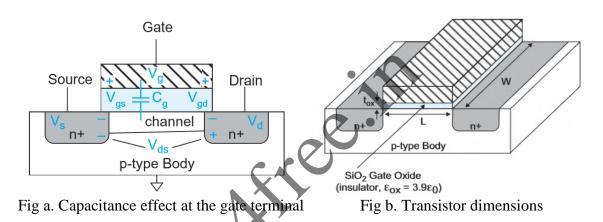

- A pMOS transistor is just the opposite, consisting of p-type source and drain regions with an n-type body.

- In both the gate is the control input.

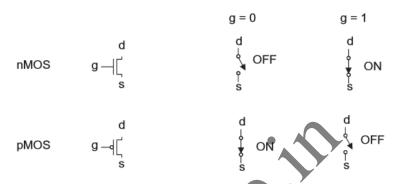

- nMOS Transistor:

- It controls the flow of electrical current between the source and drain.

- Considering an nMOS transistor, its body is generally grounded so the p-n junctions of the source and drain to body are reverse-biased. If the gate is also grounded, no current flows through the reverse-biased junctions and the transistor is OFF.

- If the gate voltage is raised, it creates an electric field that starts to attract free electrons to the underside of the Si–SiO2 interface.

- If the voltage is raised enough, the electrons outnumber the holes and a thin region under the gate called the channel is inverted to act as an n-type semiconductor.

- Hence, a conducting path is formed from source to drain and current can flow. This is the condition for transistor is ON state.

- Thus when the gate of an nMOS transistor is high, the transistor is ON and there is a conducting path from source to drain. When the gate is low, the nMOS transistor is OFF and almost zero current flows from source to drain.

- pMOS Transistor:

- The condition is reversed.

- The body is held at a positive voltage and also when the gate is at a positive voltage, the source and drain junctions are reverse-biased and no current flows, the transistor is OFF.

- When the gate voltage is reduced, positive charges are attracted to the underside of the Si–SiO2 interface. A sufficiently low gate voltage inverts the channel and a conducting path of positive carriers is formed from source to drain, so the transistor is ON.

- The symbol for the pMOS transistor has a bubble on the gate, indicating that the transistor behavior is the opposite of the nMOS.

- A pMOS transistor is just the opposite of that of nMOS. It is ON when the gate is low and OFF when the gate is high

Transistor symbols and switch-level models is shown in Fig 1.5

Fig 1.5 Transistor symbols and switch-level models

## **MOS Transistor Theory:**

- MOS transistor is a majority-carrier device current in channel between the source and drain is controlled by a voltage applied to the gate.

- In nMOS transistor majority carriers are electrons

- In pMOS transistor majority carriers are holes.

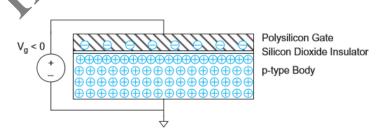

- To understand the behavior of MOS transistors, an isolated MOS structure with a gate and body but no source or drain is consider.

- It has top layer of good conducting gate layer. Middle layer is insulating oxide layer and bottom layer is the p-type substrate i.e doped silicon body. Since it is a p-type body carriers are holes

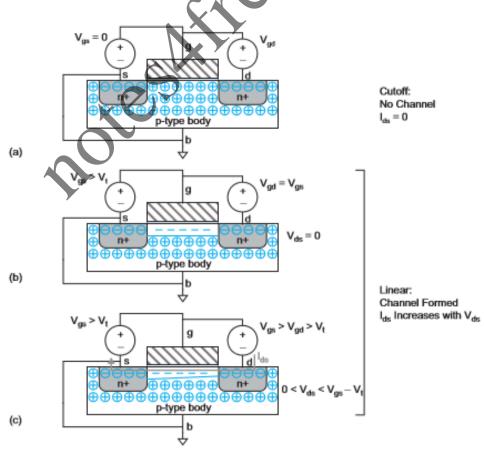

#### Fig 1.6 (a) Accumulation

- When a negative voltage is applied to the gate, the positively charged holes are attracted to the region beneath the gate. This is called the accumulation mode shown in Fig 1.6(a)

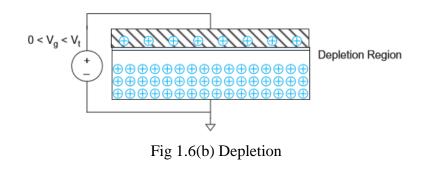

- When a small positive voltage is applied to the gate, the positive charge on the gate repels the holes resulting a depletion region beneath the gate as shown in Fig 1.6(b)

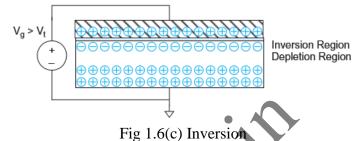

• When a higher positive potential exceeding a critical threshold voltage Vt is applied, the holes are repelled further and some free electrons in the body are attracted to the region beneath the gate. This results a layer of electrons in the p-type body is called the inversion layer.

Fig 1.7 (a) nMOS demonstrating Cutoff and Linear operation

• Now considering transistor with MOS stack between two n-type regions called the source and drain the operation is considered.

- When gate-to-source voltage, Vgs is less than threshold voltage and if source is grounded, then the junctions between the body and the source or drain are zero-biased or reversebiased and no current flows. We say the transistor is OFF, and this mode of operation is called **cutoff**. This is shown in above fig. 1.7(a)

- When the gate voltage is greater than the threshold voltage, an inversion region of electrons (majority carriers) called the channel connects the source and drain, creating a conductive path and turning the transistor ON Fig 1.7(b). The number of carriers and the conductivity increases with the gate voltage. The potential difference between drain and source is Vds= Vgs Vgd. If Vds = 0 (i.e., Vgs =Vgd), there is no electric field tending to push current from drain to source. When a small positive potential Vds is applied to the drain, current Ids flows through the channel from drain to source. This mode of operation is termed **linear, resistive, triode, nonsaturated, or unsaturated** mode as shown in Fig 1.7 (c)

- If Vds becomes sufficiently large that Vgd < Vt, the channel is no longer inverted near the drain and becomes pinched off (Fig 1.7(d)). However, conduction is still brought about by the drift of electrons under the influence of the positive drain voltage. Above this drain voltage the current Ids is controlled only by the gate voltage and ceases to be influenced by the drain. This mode is called **saturation**.

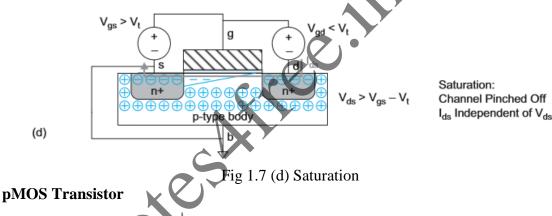

• The pMOS transistor in Fig 1.8 operates in just the opposite fashion. The n-type body is tied to a high potential so the junctions with the p-type source and drain are normally reverse-biased. When the gate is also at a high potential, no current flows between drain and source. When the gate voltage is lowered by a threshold Vt, holes are attracted to form a p-type channel immediately beneath the gate, allowing current to flow between drain and source.

Fig 1.8 pMOS Transistor

## **Ideal I-V Characteristics:**

• Considering Shockley model, which assumes the current through an OFF transistor is 0 i.e., when Vgs < Vt there is no channel and current from drain to source is 0.

- In other 2 regions (linear and saturation) channel is formed and electrons flow from source to drain at a rate proportional to electric field (field between source and drain)

- If the amount of charge in the channel and the rate at which it moves is known, we can determine the current.

- The charge on parallel plate of capacitor is given by, Q = C.V

- Here the charge in the channel is denoted by Qchannel and is given by

$Qchannel = Cg \cdot Vc$

Where Cg – capacitance of gate to the channel

Vc – amount of voltage attracting charge to the channel

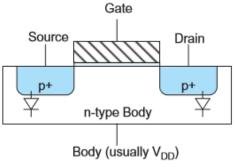

• If we model the gate as a parallel plate capacitor, then capacitance is given by Area/Thickness

• If gate is having length L and width W and the oxide thickness is tox, as shown in Fig b, the capacitance is given by

$Cg = \underbrace{\frac{\varepsilon_{ox} W L}{tox}}_{tox}$ Where  $\varepsilon_{ox}$  is the permittivity of oxide and it is 3.9  $\varepsilon_{o.}$  $\varepsilon_{o}$  is permittivity of free space,  $8.85 \times 10^{-14}$  F/cm,

- Often, the Eox/tox term is called Cox, the capacitance per unit area of the gate oxide.

- Thus capacitance is now Cg = Cox W L

- Now the charges induced in channel due to gate voltage is determined by taking the average voltage between source and drain (Fig. a) and it is given by Vc = (Vs + Vd)/2

To form the channel and carriers to flow, the voltage condition at source and drain is as follows:

$$Vs = Vgs - Vt$$

$Vd = (Vgs - Vt) - Vds$

Thus average voltage is now

$$Vc = \frac{(Vgs - Vt) + (Vgs - Vt) - Vds}{2}$$

Upon simplification, Vc is now Vc = (Vgs - Vt) - Vds/2

Thus  $Qchannel = C_{ox}WL[(Vgs - Vt) - Vds/2]$

• The velocity of charge carrier in the channel is proportional to lateral electric field (field between source and drain) and it is given by,

$$v = \mu E$$

Where  $\boldsymbol{\mu}$  is the proportionality constant called 'mobility'

• The electric field E is the voltage difference between drain and source to the length of channel. Given by,

$$E = \frac{Vds}{L}$$

• The current in the channel is given by the total amount of charge in channel and time taken by them to cross. The time taken is given by length to velocity.

i.e.,

$$Ids = \frac{total charge}{time to cross channel} = \frac{Qchannel}{L/v}$$

$$Ids = \frac{Cg.Vc}{L} v = \frac{Cg.Vc}{L} \mu E$$

$$Ids = \frac{Cg.Vc}{L} \mu \left(\frac{Vds}{L}\right)$$

$$Ids = \frac{Cox W L \left[(Vgs-Vt) - \frac{Vds}{L}\right]}{L} \mu \left(\frac{Vds}{L}\right)$$

Upon simplification, Ids is given by:

$$Ids = \mu Cox \frac{W}{L} \left[ (Vgs - Vt) - \frac{Vds}{2} \right] Vds$$

$$Ids = \beta \left[ (Vgs - Vt) - \frac{Vds}{2} \right] Vds$$

Where  $\beta = \mu Cox \frac{W}{L}$

- The above equation for current describes linear region operation for Vgs > Vt

- When Vds is increased to larger value i.e., Vds > Vsat = Vgs Vt, the channel is no longer inverted and at the drain channel gets pinched off.

- Beyond this is the drain current is independent of Vds and depends only on the gate voltage called as saturation current.

- The expression for the saturation current is given by

$$Ids = \mu Cox \frac{W}{L} \left[ (Vgs - Vt) - \frac{Vds}{2} \right] Vds$$

$$Ids = \mu Cox \frac{W}{L} \left[ (Vgs - Vt) - \frac{(Vgs - Vt)}{2} \right] (Vgs - Vt)$$

$$Ids = \mu Cox \frac{W}{L} \left[ \frac{(Vgs - Vt)}{2} \right] (Vgs - Vt)$$

$$Ids = \beta/2 (Vgs - Vt)^{2}$$

$$Where \beta = \mu Cox \frac{W}{L}$$

Summarizing the currents in all the 3 regions is

Ids = 0for Vgs < Vt cutoff

$$Ids = \beta \left[ (Vgs - Vt) - \frac{Vds}{2} \right] Vds$$

for Vds < (Vgs-Vt) linear region $Ids = \beta \left[ (Vgs - Vt) - \frac{Vds}{2} \right] Vds$ for Vds > (Vgs-Vt) saturation region

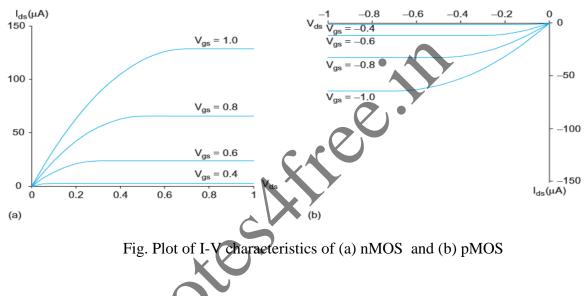

The plot of current and voltage i.e., I-V Characteristics is shown in the fig.

### pMOS Transistor:

pMOS transistors behave in the same way, but with the signs of all voltages and currents reversed. The I-V characteristics are in the third quadrant, as shown in Fig.

## Non ideal I-V Effects:

• The ideal I-V model does not consider many effects that are important to modern devices. These effects are as follows:

## Velocity saturation:

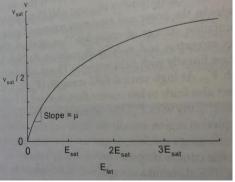

- Electron velocity is related to electric field through mobility by the equation

- $v = \mu E$ , where E is the lateral electric field or field between drain and source.

- It is assumed that  $\mu$  is constant and independent parameter w.r.t, E

- At higher E, µ is no more constant and it varies and is due to velocity saturation effect

- When electric field reaches a critical value say  $E_{sat}$ , the velocity of charge carriers tend to saturate due to scattering effect at  $E_{sat}$ . This is shown in graph below.

- The impact of velocity saturation is modelled as follows:

Before the velocity reaches critical value,

$$v = \frac{\mu \, Elat}{1 + \frac{Elat}{Esat}}$$

When the velocity reaches critical and greater it is given by,

$$v = Vsat$$

Fig. carrier velocity vs electric field

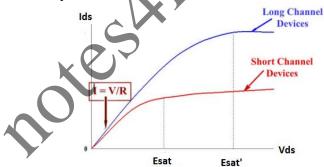

• When transistor is not velocity saturated, current Ids is given by

$$Ids = \mu Cox \frac{W}{L} \frac{(Vgs - Vt)^2}{2}$$

and with velocity saturation, current Ids is given as

$$Ids = Cox W (Vgs - Vt)Vsat$$

Observing both the expression we can say that

Ids depend quadratically on voltage without saturation and depends linearly when fully saturated

• As shown in graph for short channel devices it has extended saturation region (from Esat to Esat') due to velocity saturation.

• As channel length becomes shorter, lateral electrical field increases and transistor becomes more velocity saturated and this decreases drain current Ids.

## **Mobility degradation:**

- Velocity of charge carriers depend on electric field and when these carriers travel along the length of channel, they get attracted to the surface (i.e., Gate) by the vertical electric field (field created by gate voltage)

- Hence they bounce against the surface during their travel

- This reduces surface mobility in comparison with the mobility along the channel.

- This is known as mobility degradation and has an impact on I-V characteristics.

- As mobility decreases the current also decreases.

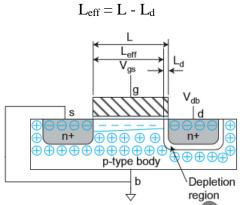

## **Channel length Modulation:**

• Ideally drain current Ids is independent on Vds in the saturation region making transistor a perfect current source.

- When Vds is increased further, near the drain barrier is build due to depletion region and reduces the length of the channel.

- This results in reducing the length of the channel by  $L_d$ . This is shown in Fig below. Thus in saturation the effective channel length is modelled as

Fig. Channel length modulation in saturation mode

- To avoid introducing the body voltage into our calculations, assume the source voltage is close to the body voltage so Vdb ~ Vds. Hence, increasing Vds decreases the effective channel length. Shorter channel length results in higher current; thus, Ids increases with Vds in saturation

- This is modeled as

$$Ids = \frac{\beta}{2} (Vgs - Vt)^2 (1 + \lambda Vds)$$

Where  $\lambda$  is empirical channel length modulation factor

• The equation can also be written as  $Ids = \frac{\mu Cox}{2} \frac{W}{L} (Vgs - Vt)^2 (1 + \lambda Vds)$ Thus as L decreases W/L ratio increases, this in turn increases Ids. Thus transistor in saturation is no more a constant current source.

Note: Channel length modulation is important in analog designs as it reduces the gain of the amplifier. But for digital circuits channel length modulations has no much importance.

## **Body Effect:**

- MOSFETs have 4<sup>th</sup> implicit terminal called body/substrate along with gate, source and drain.

- The threshold voltage Vt which is assumed to remain constant is no more a constant value and varies as potential between source and body is varied. This effect is called body effect.

- The variation in the threshold voltage is modeled by the equation

$$V_t = V_{t0} + \gamma \left( \sqrt{\phi_s + V_{sb}} - \sqrt{\phi_s} \right)$$

Where Vto is the threshold voltage when source and body are at same potential  $\Phi_s$  is the surface potential

$\gamma$  is the body effect coefficient and these two are given by Vsb is the source to body potential

$$\phi_{s} = 2v_{T} \ln \frac{N_{A}}{n_{i}}$$

$$\gamma = \frac{t_{\text{ox}}}{\varepsilon_{\text{ox}}} \sqrt{2q\varepsilon_{\text{si}}N_{A}} = \frac{\sqrt{2q\varepsilon_{\text{si}}N_{A}}}{C_{\text{ox}}}$$

$v_T$  is voltage at room temperature ( $v_T = KT/q$  at  $30^0$  it is 26mV) N<sub>A</sub> is the doping concentration level n<sub>i</sub> is the intrinsic carrier concentration q is charge (q =  $1.6 \times 10^{-19}$  C) tox oxide thickness Eox is the permittivity of oxide and is given by 3.9 Eo, where Eo is the permittivity of free space =  $8.825 \times 10^{-14}$  F/cm

Esi is the permittivity of silicon and given by 11.7 Eo and Eo= $8.825 \times 10^{-14}$  F/cm

- Body effect parameter γ depends on doping level concentration, thus by varying γ threshold voltage can be varied

- Also Vt depend on Vsb thus by proving appropriate potential threshold voltage can be varied.

- Thus a proper body bias can intentionally be applied to alter the threshold voltage, permitting trade-offs between performance and subthreshold leakage current

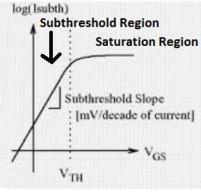

#### Subthreshold Conduction:

- The ideal I-V model assumes current flows from source to drain only when Vgs >Vt (when gate voltage is high). But in practical transistors, current does not abruptly cut off below threshold, but rather drops off exponentially.

- This regime of Vgs <Vt is called weak inversion/ subthreshold.

- This conduction of current is known as leakage and is undesired when the transistor is off

- The subthreshold conduction is modeled using equation given below

$$Ids = Idso \ e^{\frac{Vgs - Vt}{nVT}} \left[ 1 - e^{\frac{-Vds}{VT}} \right]$$

$$Ids = Idso \ e^{\frac{Vgs - Vt}{nVT}} \left[ 1 - e^{\frac{-Vds}{VT}} \right]$$

and

$$I_{ds0} = \beta v_T^2 e^{1.8}$$

$I_{dso}$  is the current at saturation and is dependent on process and device geometry Vt is the threshold voltage and  $v_T$  voltage at room temperature.

- In the expression Ids is 0 if  $V_{ds}$  is 0 and increases to full when  $V_{ds}$  is few multiples of  $\upsilon_T$

- Graph shows conduction in the subthreshold region

Fig. Subthreshold conduction

• Subthreshold conduction is useful for designing low power analog circuits and dynamic circuits as it reduces threshold voltage and results in low power consumptions.

## Drain Induced Barrier Lowering (DIBL):

- As the drain voltage Vds is increased it creates an electric field that affects the threshold voltage.

- This effect is called drain-induced barrier lowering (DIBL) and this effect is especially pronounced in short-channel transistors.

- As the channel length decreases, the DIBL effect shows up and the variation caused in the threshold voltage can be modeled as

$$V_t = V_{t0} - \eta V_{ds}$$

$\eta$  is the DIBL coefficient

## Junction Leakage:

• The MOS structure is considered there exists p-n junctions between diffusion and the substrate. With CMOS structures p-n junctions between diffusion and the substrate or well, forming diodes, as shown in Fig. The well-to-substrate junction is another diode.

Fig. CMOS structure showing formation of p-n junctions between diffusion and substrate and also between well and substrate

- The substrate and well are tied to GND or  $V_{DD}$  so that these diodes does not get into forward biased condition until voltage is applied in normal operation.

- But in reverse-biased conditions these diodes still conduct a small amount of current I<sub>D</sub>. This leakage current is modeled using equation

$$I_D = I_S \left( e^{\frac{V_D}{v_T}} - 1 \right)$$

Where,  $I_D$  is the diode current

Is is the diode reverse bias saturation current

V<sub>D</sub> is the diode voltage (either Vsb or Vdb)

- Is depends on doping levels and on the area and perimeter of the diffusion region (geometry) and  $V_{\rm D}$

- Leakage current usually lies in the range of 0.1 0.01 fA/ $\mu$ m<sup>2</sup>, which is negligible when compared to other leakage currents.

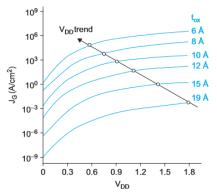

## **Tunneling (Focoler Nordheium Tunneling):**

- According to quantum mechanics, for thinner gate oxides there is a nonzero probability that an electron in the gate will find itself on the other side of the oxide, (i.e., in the region below gate/ channel).

- This effect of carriers crossing a thin barrier is called tunneling, and results in leakage current through the gate called gate leakage current.

- Thus gate oxide cannot be considered as an ideal insulator. This effects the circuit functionality and increases power consumption due to static gate current.

• Fig shows plot of gate leakage current density J<sub>G</sub> against voltage for different oxide thickness. It can be observed that as oxide thickness decreases the leakage current density increases.

Fig. plot of gate leakage current density vs voltage for different tox

• Research is going on in finding an alternate to silicon dioxide and silicon nitrate is one contender for this.

Note: As mobility of electrons is more than holes in silicon, tunneling current magnitude for nMOS is more compared pMOS.

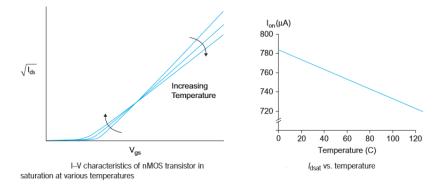

#### **Temperature Dependence:**

- Transistor characteristics are influenced by temperature

- Carrier mobility decreases with temperature and this is modeled using the relation  $(-)^{-k_{r}}$

$$\boldsymbol{\mu}(\boldsymbol{T}) = \boldsymbol{\mu}(T_r) \left(\frac{T}{T_r}\right)^{-1}$$

where T is absolute temperature, Tr is room temperature,  $k_{\mu}$  is fitting constant.

Threshold voltage + magnitude of threshold voltage decreases linearly with temperature and can be modeled as

$V_t(T) = V_t(T_r) - k_{vt}(T - T_r)$

where  $k_{vt}$  is typically about 1–2 mV/K.

- Junction Leakage increases with temperature because Is (diode reverse bias current) strongly depends on temperature

- Velocity saturation occurs sooner with temperature.

- With increase in temperature drain current decreases with temperature when transistor is ON and when transistor is OFF, the junction leakage and subthreshold conduction contribute to leakage current and this increase. This condition is shown in the graph.

- However, the circuit performance can be improved by providing cooling systems like heat sinks, water cooling, thin film refrigerator and liquid nitrogen.

- Advantages of using at lower temperatures are

- 1. Leakages can be reduced

- 2. With lower temperature, reducing threshold voltage it can be used in power saving

- 3. Most wear out mechanisms are temperature dependent and if used at lower temp they are more reliable

#### **Geometry Dependence:**

- The layout designer would draws transistors with width and length W<sub>drawn</sub> and L<sub>drawn</sub>.

- While mask preparation the actual gate dimensions may differ by X<sub>W</sub> and X<sub>L</sub>.

- While diffusion process, the source and drain would tend to diffuse laterally under the gate by L<sub>D</sub>, causing a smaller effective channel length that the carriers must traverse between source and drain. Similarly, W<sub>D</sub> accounts for smaller width while diffusion.

- Combing all these factors transistor, lengths and widths that should be used in place of L and W is given by

$$L_{\text{eff}} = L_{\text{drawn}} + X_L - 2L_D$$

$$W_{\text{eff}} = W_{\text{drawn}} + X_W - 2W_D$$

• If there is variations in the length and width of the transistor there will be variations in the performance. For example, if the currents have to be matched then length should not be varied.

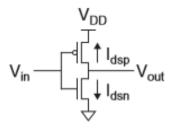

## **DC Transfer Characteristics**

• DC transfer characteristics of a circuit relate the output voltage to the input voltage, assuming the input changes slowly enough that capacitances have plenty of time to charge or discharge,

**CMOS** Inverter Static Characteristics

Fig 1.9 CMOS Inverter

CMOS inverter shown in Fig 1.9. Table below outlines various regions of operation for the n- and p-transistors. In this table, Vtn is the threshold voltage of the n-channel device, and Vtp is the threshold voltage of the p-channel device. Note that Vtp is negative. The equations are given both in terms of Vgs/Vds and Vin/Vout. As the source of the nMOS transistor is grounded, Vgsn = Vin and Vdsn = Vout. As the source of the pMOS transistor is tied to  $V_{DD}$ , Vgsp =Vin –  $V_{DD}$  and Vdsp =Vout –  $V_{DD}$ .

|      | Cutoff                         | Linear                              | Saturated                           |

|------|--------------------------------|-------------------------------------|-------------------------------------|

| nMOS | $V_{gsn} < V_{tn}$             | $V_{gsn} > V_{tn}$                  | $V_{gsn} > V_{tn}$                  |

|      | $V_{\rm in} < V_{tn}$          | $V_{\rm in} > V_{tn}$               | $V_{\rm in} > V_{tn}$               |

|      |                                | $V_{dsn} < V_{gsn} - V_{tn}$        | $V_{dsn} > V_{gsn} - V_{in}$        |

|      |                                | $V_{\rm out} < V_{\rm in} - V_{tn}$ | $V_{\rm out} > V_{\rm in} - V_{tn}$ |

| pMOS | $V_{gsp} > V_{tp}$             | $V_{gsp} < V_{tp}$                  | $V_{gsp} < V_{tp}$                  |

|      | $V_{\rm in} > V_{tp} + V_{DD}$ | $V_{\rm in} < V_{tp} + V_{DD}$      | $V_{\rm in} < V_{tp} + V_{DD}$      |

|      |                                | $V_{dsp} > V_{gsp} - V_{tp}$        | $V_{dsp} < V_{gsp} - V_{tp}$        |

|      |                                | $V_{\rm out} > V_{\rm in} - V_{tp}$ | $V_{\rm out} < V_{\rm in} - V_{tp}$ |

- The objective is to find the variation in output voltage (Vout) as a function of the input voltage (Vin). This may be done graphically, for simplicity, we assume Vtp = -Vtn and that the pMOS transistor is 2–3 times as wide as the nMOS transistor so  $\beta n = \beta p$ .

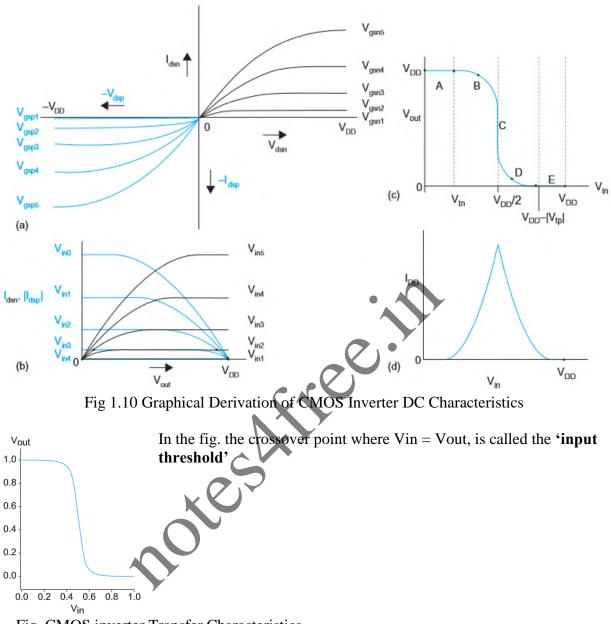

- The plot shows Idsn and Idsp in terms of Vdsn and Vdsp for various values of Vgsn and Vgsp using drain current equation.

- Fig 1.10(b) shows the same plot of Idsn and |Idsp| now in terms of Vout for various values of Vin. The possible operating points of the inverter, marked with dots, are the values of Vout where Idsn = |Idsp| for same Vin.

- These operating points are plotted on Vout vs. Vin axes in Fig. (c) to show the inverter DC transfer characteristics.

- The supply current  $I_{DD} = Idsn = |Idsp|$  is also plotted against Vin in Fig (d) showing that both transistors are momentarily ON as Vin passes through voltages between GND and  $V_{DD}$ , resulting in a pulse of current drawn from the power supply.

- The operation of the CMOS inverter can be divided into five regions indicated on Fig 1.10(c). The state of each transistor in each region and state of output is shown in Table 2.

- $\circ~$  In region A, the nMOS transistor is OFF so the pMOS transistor pulls the output to  $V_{\text{DD}}.$

- In region B, the nMOS transistor starts to turn ON, pulling the output down.

- In region C, both transistors are in saturation.

- In region D, the pMOS transistor is partially ON

- In region E, pMOS is completely OFF, leaving the nMOS transistor to pull the output down to GND.

| Region | Condition                                                      | p-device  | n-device  | Output                     |

|--------|----------------------------------------------------------------|-----------|-----------|----------------------------|

| Α      | $0 \leq V_{\rm in} < V_{tn}$                                   | linear    | cutoff    | $V_{\rm out} = V_{DD}$     |

| В      | $V_{tn} \leq V_{\rm in} < V_{DD}/2$                            | linear    | saturated | $V_{\rm out} > V_{DD}/2$   |

| С      | $V_{\rm in} = V_{DD}/2$                                        | saturated | saturated | $V_{ m out}$ drops sharply |

| D      | $V_{DD}/2 < V_{\mathrm{in}} \leq V_{DD} - \left V_{tp}\right $ | saturated | linear    | $V_{\rm out} < V_{DD}/2$   |

| Е      | $V_{\rm in} > V_{DD} - \left  V_{tp} \right $                  | cutoff    | linear    | $V_{\rm out} = 0$          |

Table 2. Summary of CMOS Inverter Operation

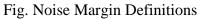

Fig. CMOS inverter Transfer Characteristics

#### **Beta Ratio Effects:**

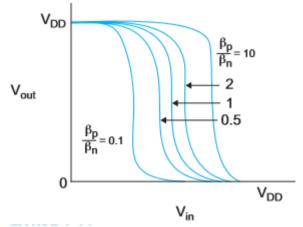

- We have seen that for  $\beta n = \beta p$  the inverter threshold voltage Vinv is V<sub>DD</sub>/2. This may be desirable because it maximizes noise margins.

- Inverters with different beta ratios  $\beta p/\beta n$  are called skewed inverters. If  $\beta p/\beta n > 1$ , the inverter is HI-skewed. If  $\beta p/\beta n < 1$ , the inverter is LO-skewed. If  $\beta p/\beta n = 1$ , the inverter has normal skew or is unskewed.

- A HI-skew inverter has a stronger pMOS transistor. Therefore, if the input is  $V_{DD}/2$ , we would expect the output will be greater than  $V_{DD}/2$ .

- LO-skew inverter has a weaker pMOS transistor and thus a lower switching threshold.

- Figure explores the impact of skewing the beta ratio on the DC transfer characteristics. As the beta ratio is changed, the switching threshold moves. However, the output voltage transition remains sharp. Gates are usually skewed by adjusting the widths of transistors while maintaining minimum length for speed.

Fig. Transfer Characteristics of Skewed Inverters

## Noise Margin:

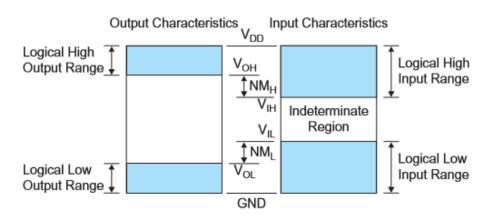

- Noise margin is closely related to the DC voltage characteristics. This parameter allows you to determine the allowable noise voltage on the input of a gate so that the output will not be corrupted.

- The specification most commonly used to describe noise margin (or noise immunity) uses two parameters: the LOW noise margin, NM<sub>L</sub>, and the HIGH noise margin, NM<sub>H</sub>.

- With reference to Fig1.12, NM<sub>L</sub> is defined as the difference in maximum LOW input voltage recognized by the receiving gate and the maximum LOW output voltage produced by the driving gate.

$$NM_{L} = V_{IL} - V_{OL}$$

• Similarly NM<sub>H</sub> is the difference between the minimum HIGH output voltage of the driving gate and the minimum HIGH input voltage recognized by the receiving gate.

$$NM_H = V_{OH} - V_{IH}$$

Where  $V_{IH}$  = minimum HIGH input voltage  $V_{IL}$  = maximum LOW input voltage  $V_{OH}$ = minimum HIGH output voltage  $V_{OL}$ = maximum LOW output voltage

• Inputs between V<sub>IL</sub> and V<sub>IH</sub> are said to be in the indeterminate region or forbidden zone and do not represent any legal digital logic levels. Therefore, it is generally desirable to have V<sub>IH</sub> as close as possible to V<sub>IL</sub> and for this value to be midway in the "logic swing,"  $V_{OL}$  to  $V_{OH}$ . This implies that the transfer characteristic should switch abruptly; that is, there should be high gain in the transition region.

• DC analysis gives us the static noise margins specifying the level of noise that a gate may see for an indefinite duration.

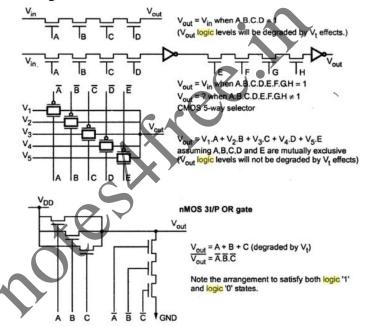

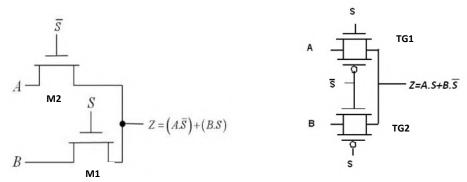

### **Pass Transistor DC characteristics:**

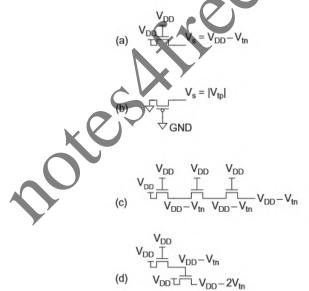

- nMOS transistors pass '0's well but 1s poorly. Figure (a) shows an nMOS transistor with the gate and drain tied to  $V_{DD}$ . Imagine that the source is initially at Vs = 0. Vgs > Vtn, so the transistor is ON and current flows. If the voltage on the source rises to  $Vs = V_{DD} Vtn$ , Vgs falls to Vtn and the transistor cuts itself OFF.

- Therefore, nMOS transistors attempting to pass a 1 never pull the source above  $V_{DD} Vtn$ . This loss is sometimes called a threshold drop.

- Similarly, pMOS transistors pass 1s well but 0s poorly. If the pMOS source drops below |Vtp|, the transistor cuts off. Hence, pMOS transistors only pull down to within a threshold above GND, as shown in Fig (b).

- As the source can rise to within a threshold voltage of the gate, the output of several transistors in series is no more degraded than that of a single transistor Fig (c).

- However, if a degraded output drives the gate of another transistor, the second transistor can produce an even further degraded output Fig(d).

Fig. Pass Transistor Threshold drop

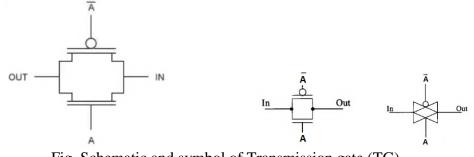

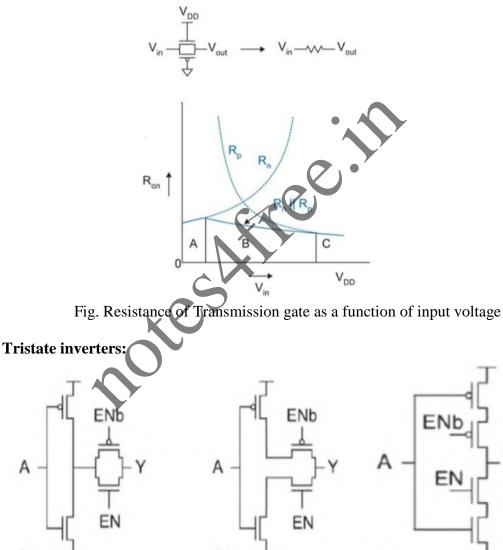

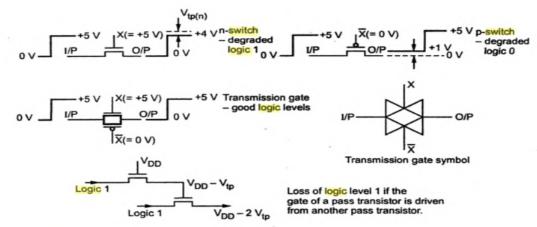

- The problem seen with nMOS and pMOS of not passing strong 1's and strong 0's respectively can be overcome by using Transmission gate.

- It has an nMOS and pMOS connected in parallel as shown in fig below.

Fig. Schematic and symbol of Transmission gate (TG)

- When A is logic high both transistors are ON and TG is said to be ON. When input is provided as nMOS is not able to transmit strong 1, pMOS will do the function. Similarly when pMOS is not able to transmit strong 0, nMOS will do this function.

- Thus transmission gate is able to send both strong 0 and strong 1 without any signal degradation.

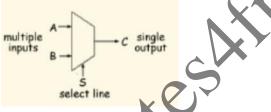

- Transmission gate can be used as

- o Multiplexing element

- Analog switch

- o Latch element

• By cascading a transmission gate and an inverter forms a tristate inverter as shown in Fig (a)

(c)

- When EN = 1, EN'= 0, thus transmission gate is ON and transmits the output Y as the compliment of inverter input A.

- When EN = 0 and EN' =1, transmission gate is OFF and the output Y is in tristate or high impedance state.

- Fig (b) and (c) shows other configurations of tristate inverters

(b)

(a)

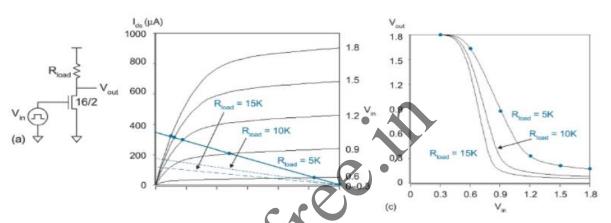

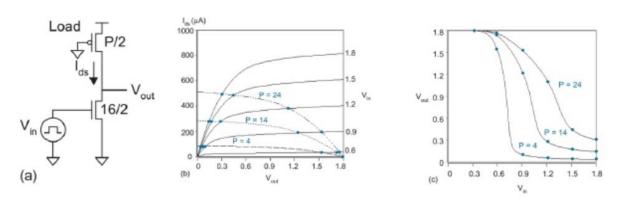

#### **Ratioed Inverters Transfer Characteristics**

- Other than CMOS inverter there are also other forms of inverters. One such is shown in the fig. below which has an nMOS with load as resistor.

- This is an nMOS inverter circuit. When Vin = 0, nMOS is OFF and output goes to Vdd through the Rload.

- When Vin = 1, nMOS is ON and pulls the output to gnd.

- When we consider the transfer characteristics and I-V characteristics, we see that as load is increased  $V_{OL}$  decreases also the current decreases. Thus choosing load resistor compromises between current and  $V_{OL}$ .

Fig. nMOS inverter with resistive load, I-V characteristics and transfer characteristics

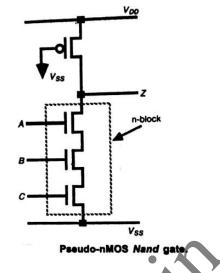

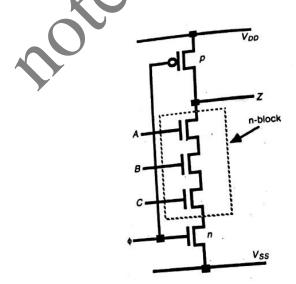

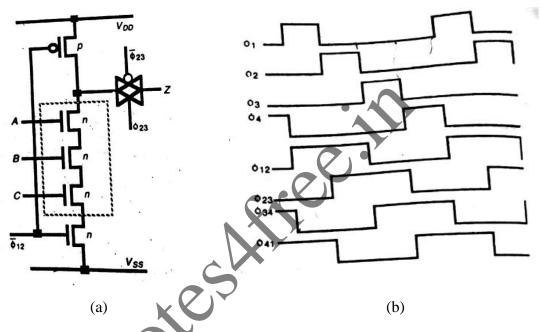

- An alternate to this is using a more practical circuit called pseudo-nMOS inverter circuit, which uses a pMOS transistor as a load with its gate terminal always grounded.

- Here pMOS will be in ON state. When Vin = 0, nMOS is OFF and as pMOS is ON the output rises to Vdd. When Vin = 1, nMOS will be ON and pulls the output to gnd.

- When the transfer characteristics is observed as the W/L ratio is varied for pMOS in the pseudo-nMOS inverter circuit, the shape of the transfer characteristics varies.

- As parameter P (i.e., as W is decreased sharper characteristics is obtained) is varied characteristics varies with higher value of P less sharper characteristics is seen.

- In the circuit P/2 represents the W/L ratio.

Fig. pseudo-nMOS inverter with I-V characteristics and transfer characteristics

- These types of gates are called as ratioed circuits as transfer function depends on the strength of pull down (pMOS) to pull up (nMOS) devices.

- In these types of circuits ratios must be chosen properly so that circuit operates properly.

- Disadvantage seen with these ratioed circuits are

- Constant power dissipation

- Poor noise margin

- However these circuits are used under limited circumstances such as reduced input capacitance and smaller area.

## Fabrication

## nMOS Fabrication:

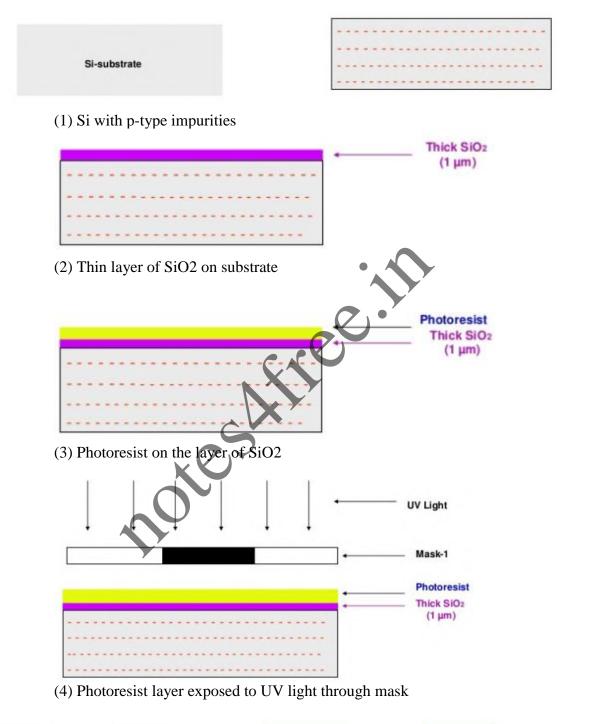

Semiconductor device fabrication is the process of creating integrated circuits in multiplestep sequence of photolithographic and chemical processing during which electronic circuits are gradually created on a wafer made of pure semiconducting material.

The following steps gives general aspect of pMOS fabrication process.

- 1. Processing is carried on thin wafer cut from single silicon crystal of high purity to which p-type impurities are introduced as crystal is grown. Wafers are around 75 to 150 mm in diameter and 0.4 mm thick. They are doped with boron (p-type) impurity concentration of  $10^{15}/\text{cm}^3$  to  $10^{16}$  /cm<sup>3</sup>.

- 2. On this a thick layer if silicon dioxide (SiO2) of 1µm. This protects the surface, act as barrier to dopants and also act as an insulating layer on which other layers can be deposited and patterned.

- 3. The surface is now covered with photoresist and it is spun to achieve even distribution of required thickness.

- 4. A mask is used and the photoresist layer on the wafer is exposed to UV light. Mask defines those regions into which diffusion will take place and these regions remain unaffected after exposing to UV light and other region gets hardened.

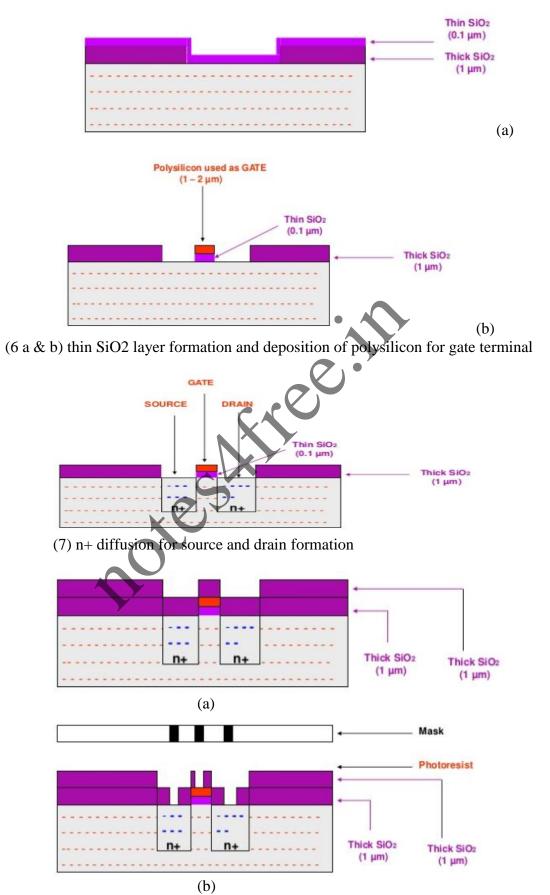

- 5. The UV exposed regions are etched away along with the silicon dioxide layer so that the wafer surface is exposed in the window defined by the mask.

- 6. The remaining photoresist is removed and a thin layer of SiO2 is grown over entire surface and then polysilicon is deposited on top of this to form gate structure.

- 7. The thin oxide is removed to expose areas into which n-type impurities are diffused to form source and drain.

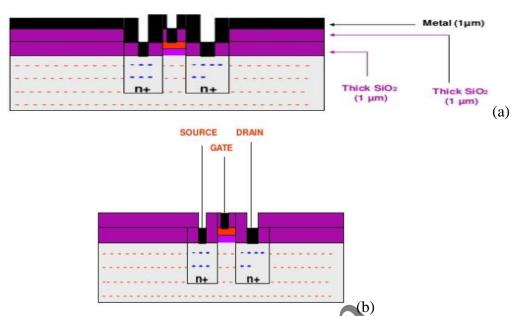

- 8. Thick oxide is grown all over again and then masked with photoresist and etched to expose selected area of polysilicon gate and drain and the source areas where connections are to be made.

- 9. The whole chip is then has metal (Al) deposited over its surface to a thickness of 1µm. This metal layer is then masked and etched to form the required interconnection pattern.

Fig below depicts the nMOS fabrication steps:

(5) UV exposed regions are etched away

8(a & b) thick layer of SiO2 grown and masked with photoresist S and D contact cuts

9(a & b) metal layer deposition and metal layer is masked and etched to form final nMOS transistor

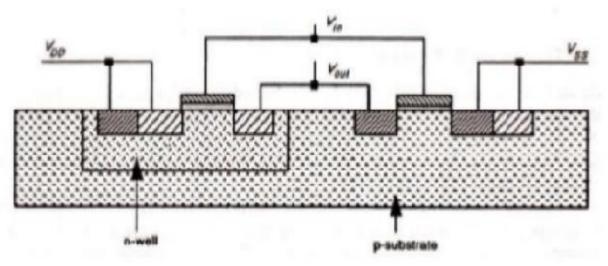

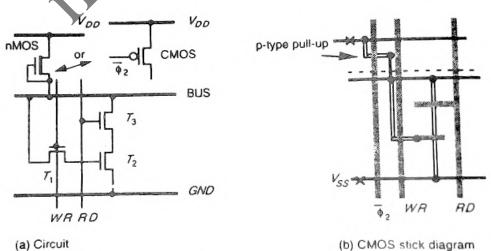

## **CMOS Fabrication**

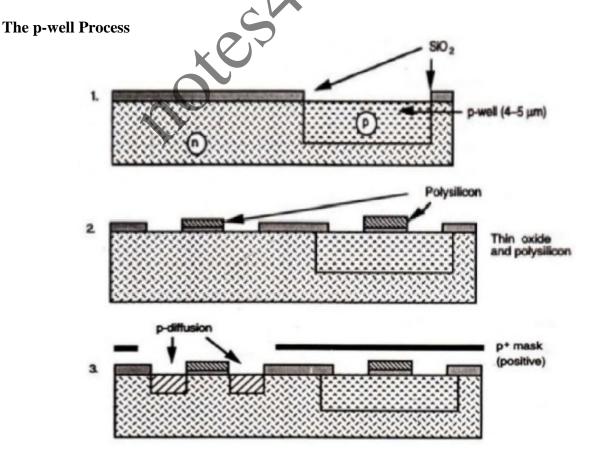

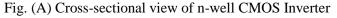

- There are a number of methods for CMOS fabrication, which includes p-well, n-well, twin tub and silicon-on-insulator (SOI) processes.

- The p-well process is widely used and the n-well process as it is an retrofit to existing nMOS technology.

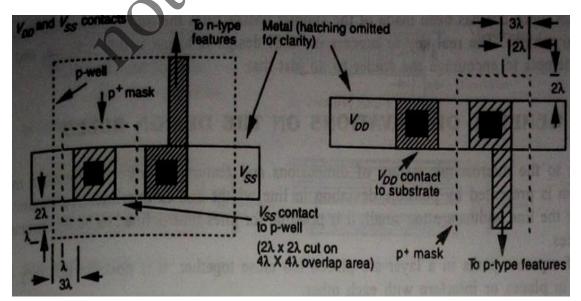

Fig. CMOS p-well inverter showing  $V_{DD}$  and  $V_{SS}$  substrate connections

• The p-well structure has an n-type substrate in which p-type devices can be formed with the help of masking and diffusion. In order to accommodate n-type devices, deep p-well is diffused into the n-type substrate. This is shown in Fig 1.

Masking, patterning and diffusion process is same as that of nMOS fabrication. The summary of processing steps are:

- Mask: defines the areas in which the deep p-well diffusion has to take place.

- Mask 2: defines the thin oxide region (where the thick oxide is to be removed or stripped and thin oxide grown)

- Mask 3: patterning the polysilicon layer which is deposited after thin oxide.

- Mask 4: A p+ mask is used (to be in effect "AND" with mask 2) to define areas where p-diffusion is to take place.

- Mask 5: -ve form of mask 4 (p+ mask) is used which defines areas where ndiffusion is to take place.

- Mask 6: Contact cuts are defined using this mask.

- Mask 7: The metal layer pattern is defined by this mask.

- Mask 8: An overall passivation (over glass) is now applied and it also defines openings for accessing pads.

- In the process, the diffusion should be carried out with special care as p-well concentration and depth will affect the threshold voltage and also the breakdown voltage of the n-transistor.

- To achieve low threshold voltage either deep-well diffusion or high-well resistivity is required.

- But deep well require larger spacing between n- and p-type transistors and wires due to lateral diffusion and therefore needs larger chip area.

- The p-well acts as substrate for n-devices within parent n-substrate and two areas are electrically isolated

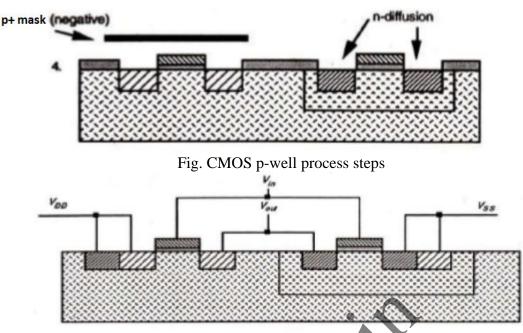

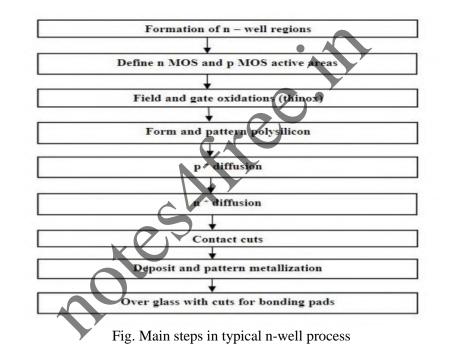

#### The n-well Process

• The p-well processes have been one of the most commonly available forms of CMOS. However, an advantage of the n-well process is that it can be fabricated on the same process line as conventional n MOS.

- n-well CMOS circuits are also superior to p-well because of the lower substrate bias effects on transistor threshold voltage and inherently lower parasitic capacitances associated with source and drain regions.

- Typically n-well fabrication steps are similar to a p-well process, except that an n-well is used which is illustrated in flow diagram

- The first masking step defines the n-well regions.

- The well depth is optimized to ensure against p-substrate to p+ diffusion breakdown without compromising the n-well to n+ mask separation.

- The next steps are to define the devices and diffusion paths, grow field oxide, deposit and pattern the polysilicon, carry out the diffusions, make contact cuts and metallization.

- An n-well mask is used to define n-well regions, as opposed to a p-well mask in a p-well process.

- Fig. Depicts inverted circuit fabricated by n-well process.

## The Twin-Tub process

- Twin-tub CMOS technology provides the basis for separate optimization of the p-type and n-type transistors, thus making it possible for threshold voltage, body effect, and the gain associated with n- and p-devices to be independently optimized.

- Generally the starting material is either an n+ or p+ substrate with a lightly doped epitaxial or epi layer, which is used for protection against latch-up.

- The aim of epitaxial is to grow high purity silicon layers of controlled thickness with accurately determined dopant concentrations distributed homogeneously throughout the layer. The electrical properties for this layer are determined by the dopant and its concentration in the silicon.

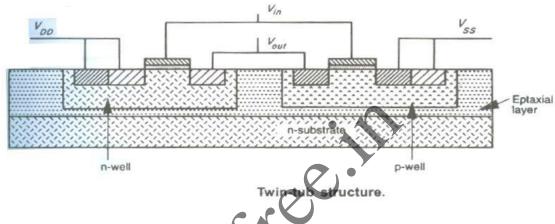

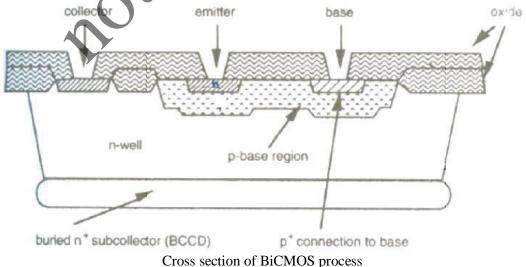

## **BiCMOS Technology**

- The load driving capabilities of MOS transistors is less because of limited current sourcing and sinking abilities of both p and n transistors

- Bipolar transistors provide high gain, better noise and high frequency characteristics than MOS transistors.

- Thus Bipolar can be combined with CMOS technology to build high speed devices called as BiCMOS devices.

Layout view of BiCMOS process.

|         | CMOS technology                         | BiCMOS technology             |  |  |

|---------|-----------------------------------------|-------------------------------|--|--|

|         |                                         |                               |  |  |

| 1.      | It has bidirectional capability (source | Essentially unidirectional    |  |  |

|         | and drain are interchangeable)          | <b>TT 1 1 1</b>               |  |  |

| 2.      | Low static power dissipation            | High power dissipation        |  |  |

| 3.      | It has high input impedance             | It has Low input impedance    |  |  |

| 4.      | High Packing Density                    | Low Packing Density           |  |  |

| 5.      | It has Low gain                         | It has High gain              |  |  |

| 6.      | High delay sensitivity to load          | Low delay sensitivity to load |  |  |

| noteski |                                         |                               |  |  |

# Module 2

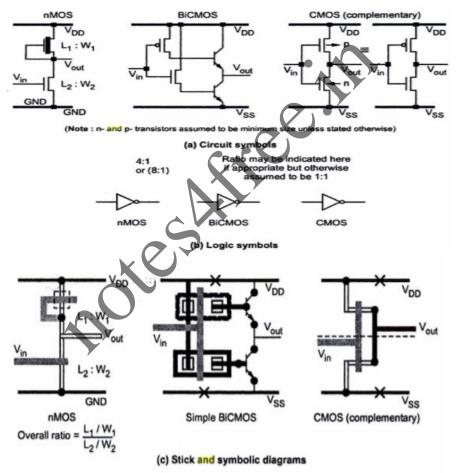

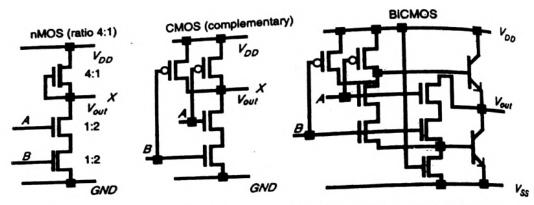

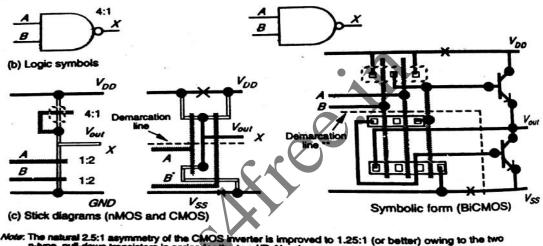

# **MOS and BiCMOS Circuit Design Processes**

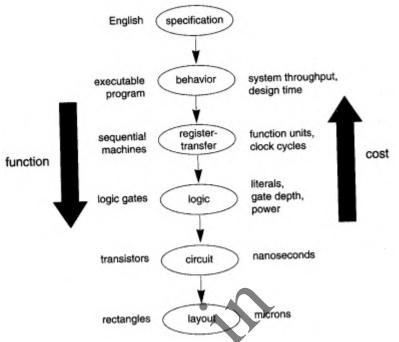

- Methods of realizing circuit design in silicon

- The design process can be understood by means of stick diagrams and symbolic diagrams along with set of design rules.

- Design rules: is a communication link between designers specifying the requirements and the fabricator.

## **MOS Layers:**

- MOS circuits are basically formed by 4 layers

- Metal

- Polysilicon

- N diffusion

- P diffusion

- Here all the 4 layers are isolated from each other through thick or thin oxide layer (i.e., silicon dioxide layer)

- The thin oxide (thinox) layer includes n-diffusion, p-diffusion and transistor channel.

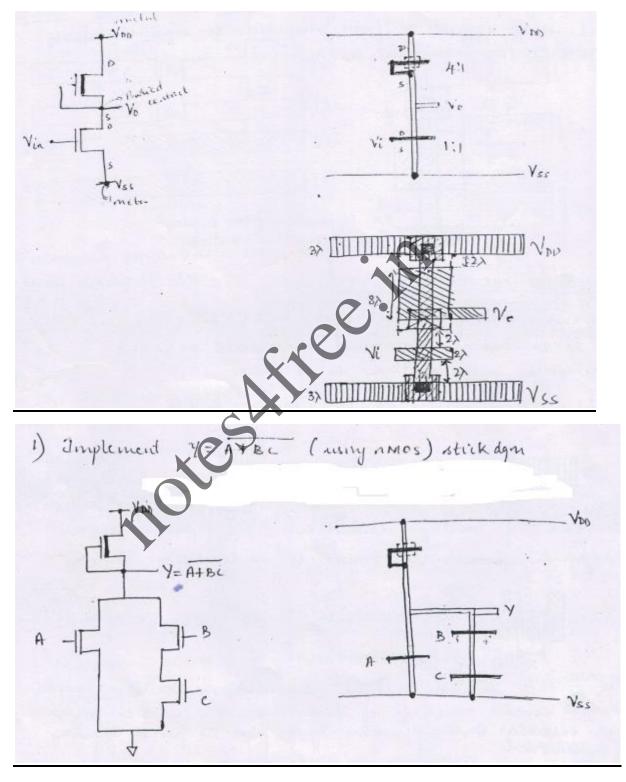

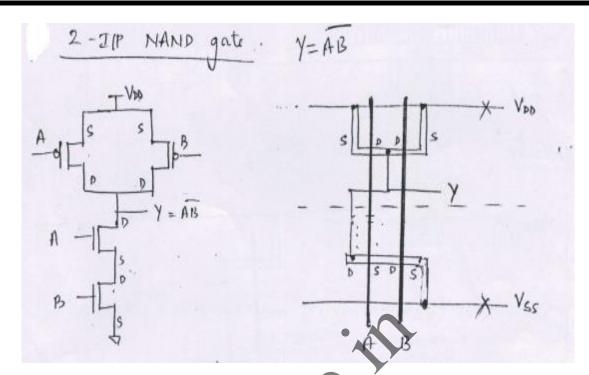

## Stick diagram:

- Stick diagrams are a means of capturing topography and layer information using simple diagrams.

- They convey layer information through color codes (or monochrome encoding).

- Acts as an interface between symbolic circuit and the actual layout.

- Stick diagrams do show all components/vias(contacts), relative placement of components and helps in planning and routing. It goes one step closer to layout.

- However they do not show exact placement of components, transistor sizes, length and width of wires also the boundaries. Thus we can say that it does not give any low level details.

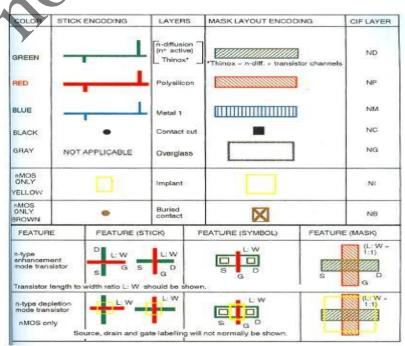

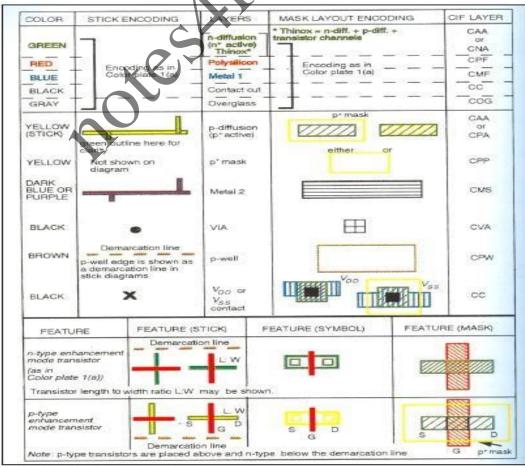

- The color encodings chosen for different technologies is shown below.

- Encodings for NMOS process:

#### **Procedure to draw Stick Diagram:**

#### **Nmos Design Process.**

1) Draw two metal lines/ power rails providing sufficient space to accommodate all transistors. i.e: Vdd & Vss.

- 2) Draw common n+ diffusion layer for all the transistors.

- 3) Provide Vdd and Vss contacts.

- 4) Draw polysilicon to cross n+ diffusion layer to form transistors.

- 5) Create buried contact for depletion transistor.

- 6) Provide input and output connection.

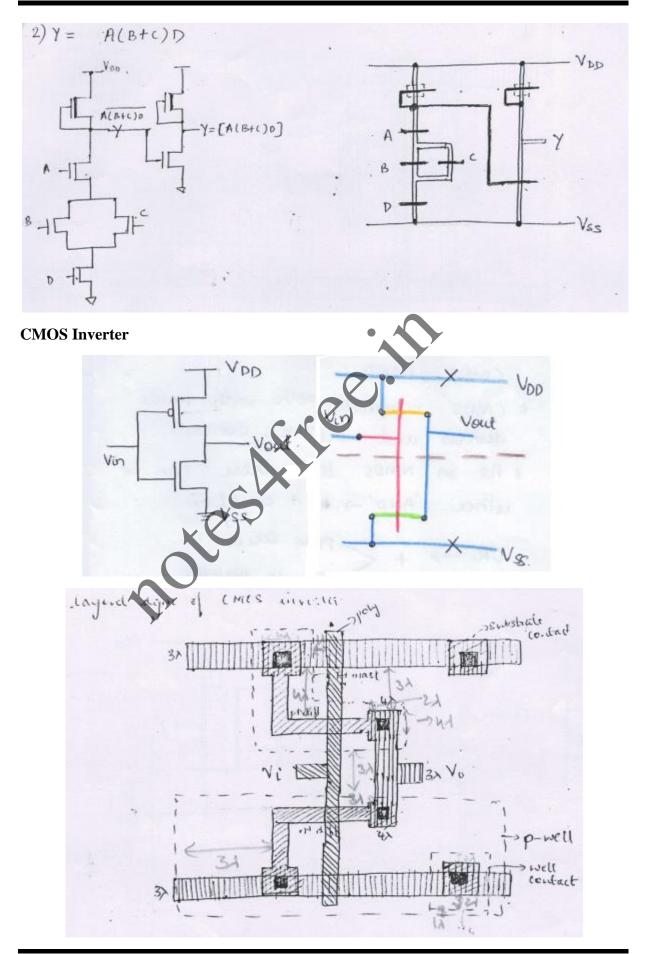

#### **CMOS Design Process:**

- Two type of transistors are used i.e: Nmos and Pmos, thus in stick diagram demarcation line is used to separate them.

- All Pmos transistors are placed above Demarcation line and Nmos transistors below demarcation line.

- While drawing stick Diagram

- 1. Diffusion paths must not cross the demarcation line

- 2. N-diffusion and P-diffusion wires must not join.

- 3. Nmos and Pmos transistors are joined by Metal layer when it is required.

- 4. Cross must be placed on Vdd and Vss which represent substrate and P-well connection respectively.

#### **Encodings for CMOS process:**

## Procedure to draw Stick Diagram:

1) Draw two metal lines/ power rails providing sufficient space to accommodate all transistors. i.e: Vdd & Vss.

- 2) Draw demarcation line in the middle of the two power lines.

- 3) Draw P+ diffusion above demarcation and N+ diffusion below demarcation

- 4) Draw polysilicon to represent Pmos and Nmos which represents gates of the transistor.

- 5) Connect source terminal of transistors to supply.

- 6) Drain terminals of transistor are connected using metal 1.

- 7) Place contact cuts wherever necessary.

- 8) Draw X which represents substrate and P-well contact on power lines.

**Layout:** describes actual layers and geometry on silicon substrate to implement a function(Expressions).

[Diffusion region where transistor can be formed is called active region, polysilicon serves as the gate of MOS transistor. L defines channel length and W represents width of channel/active region]

**Design rules:** are set of guidelines which specify minimum dimension and spacing allowed in layout drawing. Design rules also acts a communication link between circuit designers and process engineers during manufacturing phase.

**Goal of design rule:** is to achieve optimum yield. Yield = (No. of good chips on wafer)/(Total no. of chips on wafer).

Design rules are also called layout rules. If the circuit performance has to be increased then rules must be more aggressive. Else this leads to non-function of the circuit or yield reduction. There are two rules.

1. Micron Rule - Absolute Dimension rule, here all sizes and spacing are specified in micron. Here the circuit density is the important goal.

2. Lambda ( $\lambda$ ) Based Rules - The Lambda based design rules are Proposed by Mead and Conway. Scalable design rules, here this design rule normalizes all geometric design rule by parameter lambda ( $\lambda$ ) also called as scaling factor/feature size. In this all mask patterns are expressed as multiples of lambda.

Advantages of lambda based design rules:

1. The mask layout can be scaled down proportionally if the feature size of the fabrication process is reduced.

- 2. Design rules are conservative.

- 3. This rule enable technology changes and design reuse and reduced design cost.

Disadvantages:

- 1. Linear scaling cannot be extended and is limited over range of dimension (1-3  $\mu$ m)

- 2. As rules are conservative, results in over dimension and density of design is less.

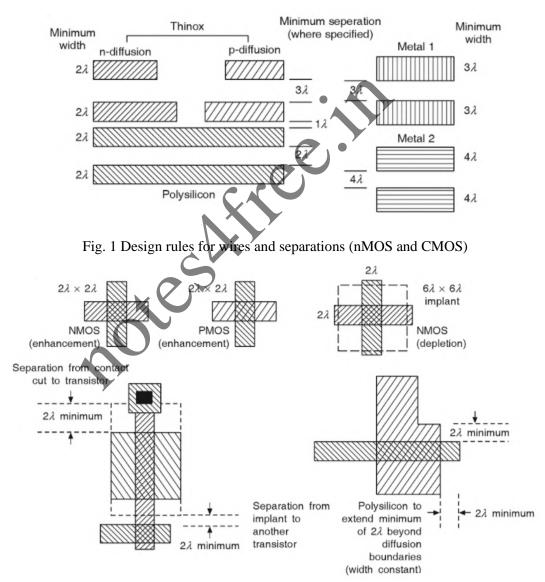

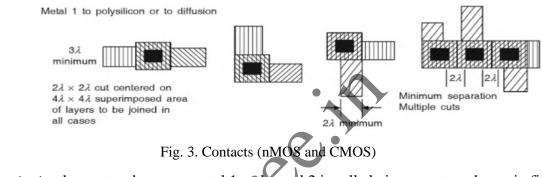

The Design rules can be conveniently set out in diagrammatic form as shown in fig. 1 for width and separation of conducting path. In fig. 2 shows the design rules associated with extensions and separations with transistor. Fig. 3 and 4 demonstrates the design rules for

contacts between layers. Table below also gives the layer and distance of separation dimensions.

| Layer       | Dimension |

|-------------|-----------|

| n-diffusion | 2λ        |

| p-diffusion | 2λ        |

| Polysilicon | 2λ        |

| Metal 1     | 3λ        |

| Metal 2     | 4λ        |

| Layer -Layer                | Dimension |

|-----------------------------|-----------|

| n-diffusion – n-diffusion   | 3λ        |

| p-diffusion – p-diffusion   | 3λ        |

| n/p diffusion - polysilicon | 1λ        |

| Poly-poly                   | 2λ        |

| Metal 1                     | 3λ        |

| Metal 2                     | 4λ        |

#### Layer dimension

**Distance of Separation**

Fig. 2 Design rules for Transistors (nMOS, pMOS and CMOS)

#### **Transistor design rules**

- Minimum dimension of transistor is  $2\lambda \times 2\lambda$  overlapping of diffusion and ploy

- Poly and diffusion both must extend beyond the boundary of transistor at least by 2λ

- Implant for depletion mode transistor is  $6\lambda \times 6\lambda$  i.e., implant must extend boundary of transistor by at least  $2\lambda$  in all direction.

- From the boundary/ implant of one transistor, the next transistor should maintain min distance of  $2\lambda$

- The distance from contact cut to transistor should be at least  $2\lambda$

**Metal contact** – contact between metal 1 to polysilicon OR metal 1 to diffusion (active region) is called metal contact. This is shown in fig. 3

- A  $2\lambda \times 2\lambda$  cut centered on  $4\lambda \times 4\lambda$  superimposed area is used to connect layers

- In case of multiple contacts the distance between adjacent contacts should be  $2\lambda$

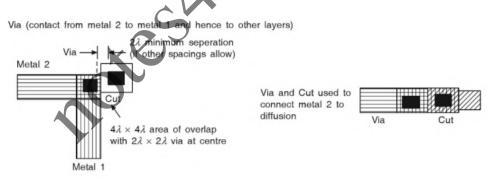

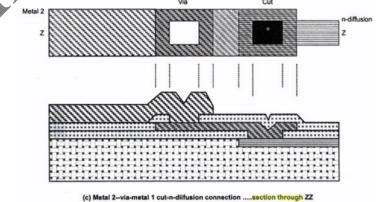

Via contact – the contact between metal 1 and metal 2 is called via contact as shown in fig. 4.

- A  $2\lambda \times 2\lambda$  cut centered on  $4\lambda \times 4\lambda$  superimposed area is used to connect layers

- To connect metal 2 with diffusion via and cut both are used

## **Contact Cuts:**

- Electrical connection between layers can be done using special structures 'contact cuts'.

- There are 3 approaches for contacts between polysilicon and diffusion in nMOS circuits. They are

- 1. Polysilicon to metal and then to diffusion

- 2. Buried contact polysilicon to diffusion

- 3. Butting contact polysilicon to diffusion using metal

- ✓ Among the three buried contact is most used as it gives economy in space and reliable contact.

- Buried contact is distinguished feature in nMOS for connection between poly and diffusion and this is most widely used than butting contact.

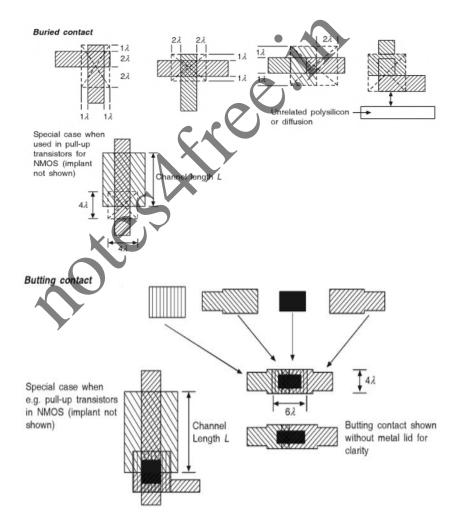

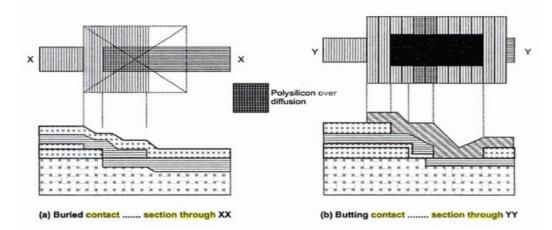

## **Buried Contact (nMOS):**

- Layer is joined over the area of 2λ × 2λ with buried contact cut extending by 1λ in all directions except in the diffusion path. It extends by 2λ in order to avoid formation of unwanted transistors.

- The contact cut shown in broken line indicates the region where thinox is removed on the silicon wafer and polysilicon gets deposited on wafer.

- When impurities are added, it diffuse into poly and also to diffusion region within the contact area. This provides satisfactory contact between ploy and diffusion as shown in fig 5.

- In CMOS poly to diffusion connections are made through metal. The process of making connection between metal and either of 2 layers (poly or diffusion) is by buried contact.

Fig. 5 Buried and butting contacts only for nMOS

Fig 5. Cross section through contact structures

#### **Butting contact**

- Butting contact process is complicated and done when two layers do not overlap. Contact cut of  $2\lambda \times 2\lambda$  is made until each of layers is joined. The layers are held in such a way that these two contacts become continuous.

- The poly and diffusion outlines overlap and thinox under ploy acts as mask during diffusion process. Finally contact between two butting layers is done by a metal. This can be seen in fig. 5 cross-sectional view.

## **Double Metal MOS Process Rules:**

- If to process considered till now introduction of second metal layer will boosts the design capabilities. It gives more freedom. Ex. this will be helpful for power rail (Vdd and Vss/Gnd) distribution and also for clock.

- This process is called Double Metal MOS Process

- This technique involves connecting metal 1 and metal 2 contacts called 'via'. This is shown in fig. 4 and fig. 6

Fig. 6 cross section of via contact structure

- The 2<sup>nd</sup> metal layer is coarser than 1<sup>st</sup> metal layer (conventional) and the isolation layer between the 2 is usually thicker than normal.

- To distinguish contacts between 1<sup>st</sup> and 2<sup>nd</sup> metal layer they are called as 'vias' rather than contact cut

- In stick diagram representation its color code is dark blue or purple.

The steps of fabrication process is as follows:

- 1. Using chemical vapor deposition oxide layer under 1<sup>st</sup> metal layer is deposited.

- 2. using same method oxide between 2 metal layers are formed.

3. Selected areas of oxide are removed by using plasma etching. The etching process is done under high vertical ion bombardment to get high and uniform etching.

The layout strategy used with double metal process is summarized as below

- 1. Second metal layer is usually used for global power railings and clock lines

- 2. First metal layer is used for local power distribution and signals.

- 3. The layout of the two metals are such that are mutually orthogonal wherever possible

- Similar to double metal process, other process allows second poly layer. The process steps are similar to previously described process.

- The first polysilicon (poly 1) layer is deposited and patterned on this a second thinox (thin oxide) layer is grown. On this the second polysilicon (poly 2) layer is deposited and patterned. Thus 2<sup>nd</sup> thinox isolated the poly layers.

- Presence of poly 2 provides greater flexibility in interconnections and allows transistors to be formed by intersection of poly 2 and diffusion.

### CMOS Lambda-based Design Rules:

- Comparing to Nmos fabrication process, CMOS fabrication is more complex.

- Extending the Nmos design rules, Noting exclusion of butting contact and buried contact rules.

- Additional rules associated with CMOS process concerned with unique feature p-well CMOS, i.e: p-well and P+ Mask and Substrate contact.

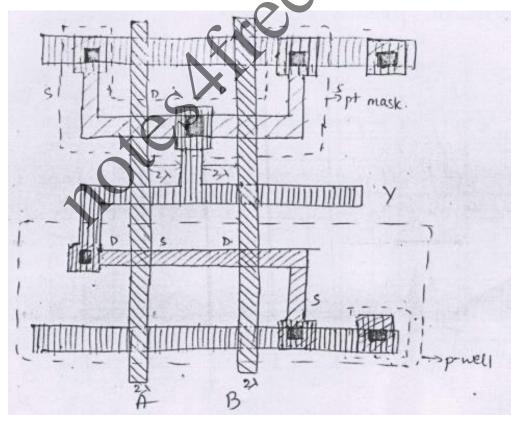

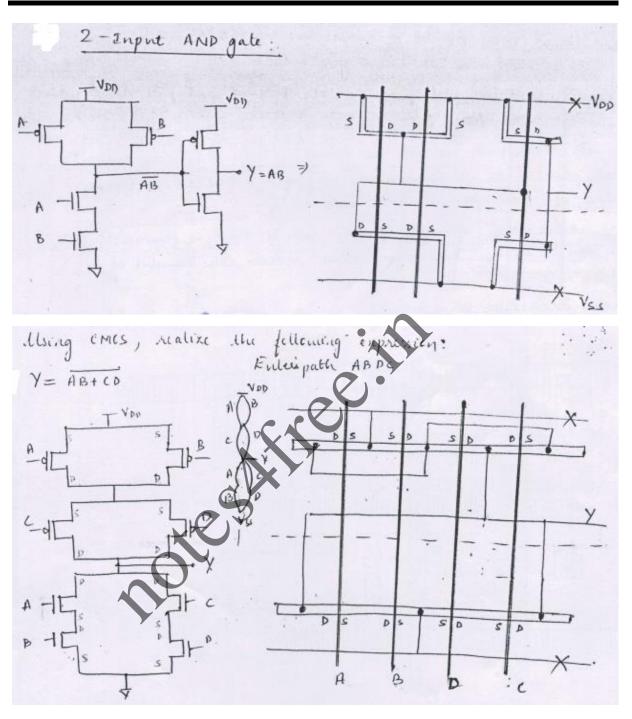

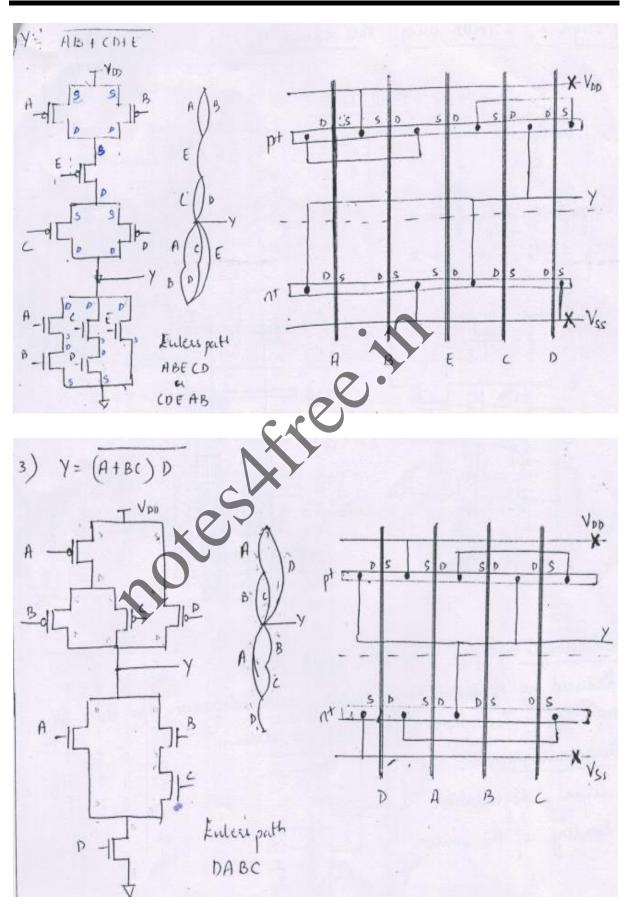

Problems on stick diagram and layouts.

## **Nmos Inverter**

Diffusion lines running horizontal and polysilicon (ines) in vertical direction.

- When more number of inputs available, Euler's path is determined to know gate ordering.

- Advantage of using Euler's path is to that a common diffusion line can be used which reduces number of contact cuts.

- Uninterrupted path in both pull-up and pull down network represents optimized gate ordering which helps in drawing layout without breaking the diffusion layer.

Dept. of ECE, SVIT

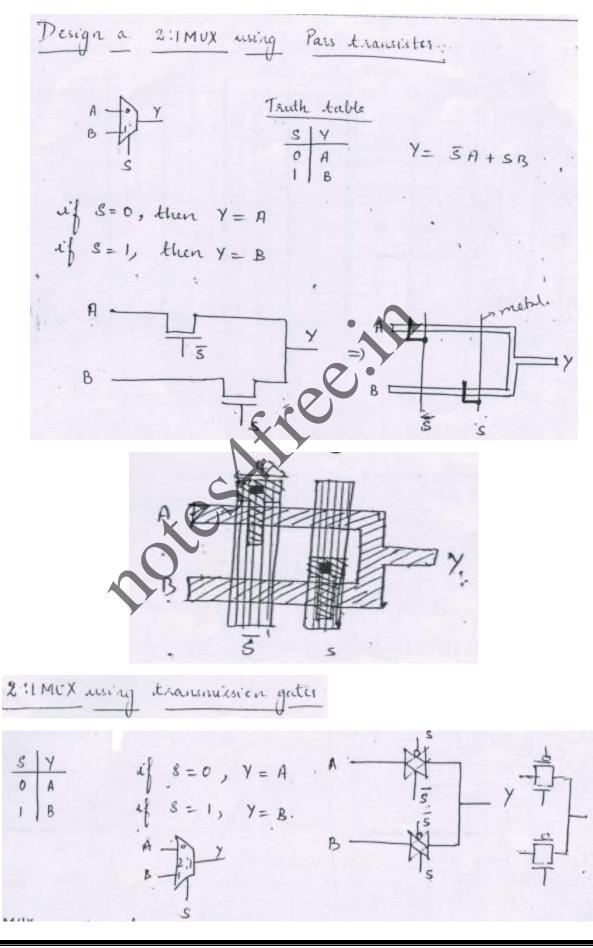

Stick diagram of 2:1 MUX using transmission gates.

Two input XOR gate realization using transmission gates.

Two way selector with enable

# **Basic circuit concepts**

- In MOS technology, Active devices are dealt with some measurement.

- Wiring up of circuits is done through various conductive layers which is produced by MOS Processing.

- Therefore it is necessary to be aware of resistive and capacitive characteristics of each layers.

- For evaluating the effects of wiring, input and output capacitances, sheet resistance and standard unit capacitances are used.

- Further delay associated with wiring, inverters are evaluated by the term delay unit  $\tau$ .

## Sheet Resistance R<sub>s</sub>

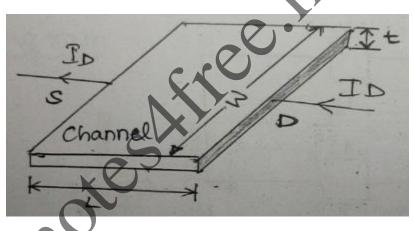

Consider a transistor with a channel having resistivity  $\rho$ , width W, thickness t and length between source and drain is L.

Resistance of the channel between drain and source is expressed as.

$$R_{DS} = \frac{\rho.Length}{Area of \ cross \ section} = \frac{\rho.L}{t.W}$$

$$R_{DS} = R_s \frac{L}{W}$$

Where  $R_s = \frac{\rho}{t}$  is a constant and it is called sheet resistance.

From the above equation, sheet resistance can be defined as resistance of the channel whose length and width are equal.

$R_s$  is completely independent of area square. Ex: 1µm per side square slab of material has exactly same resistance as 1cm per side square slab of same material if thickness is same.

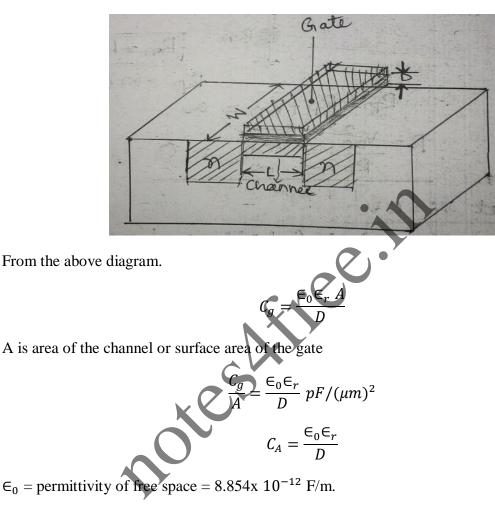

#### Area capacitance

In between gate and channel exists a capacitance and it is called gate capacitance and denoted by  $C_q$ .

$\in_r$  = relative permittivity of a given material

D = thickness of sio2 constant for a given technology.

Area capacitance is defined as capacitance per unit area at the gate of transistor and denoted by  $C_A$ .

## Standard unit of capacitance $(\Box C_g)$

The standard unit of capacitance is defined as the capacitance at the gate of 1:1 transistor.

Ex: consider a 1:1 transistor where  $L = 2\lambda$  and  $W = 2\lambda$ .

Gate area of transistor =  $L \times W$

$$A = 2\lambda x \ 2\lambda = (2\lambda)^2$$

Actual capacitance at the gate of transistor  $C = C_A$ .  $A = C_A$ .  $(2\lambda)^2$

$$C = 4x10^{-4} PF/(\mu m)^2 (2\lambda)^2$$

Consider 5  $\mu m$  technology, i.e.  $2\lambda = 5 \mu m$

$$C = 4x10^{-4} pF/(\mu m)^2$$

.  $(5 \mu m)^2 = 4x10^{-4} x 25 = 0.01 pF$

$\mathbf{C} = 1 \Box \mathcal{C}_g$

#### Standard Delay Unit (τ)

Time delay is measured in terms of standard unit  $\tau$ .

It is defined as product of  $R_s$  and  $C_g$ . i.e.  $\tau = R_s \square C_g$

#### Measurement of τ.

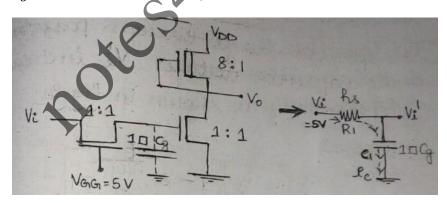

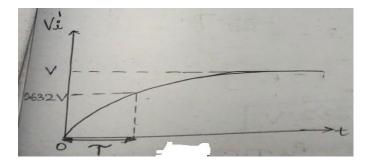

Consider nmos driven by pass transistor shown in below figure and the dimensions are indicated. Pass transistor is ON for given gate voltage  $V_{GG}$ . Pass transistor is represented by  $R_s$  due to its equal length and width. Pull down transistor of inverter is represented by capacitance  $\Box C_q$ . Since pull down has minimum dimensions.

$\tau$  is defined as time taken by capacitor to charge from 0 to 63.2% of maximum value as shown in below figure.

## **Inverter Delays**

Consider basic 4:1 nmos inverter. To achieve 4:1  $Z_{pu}$  to  $Z_{pd}$  ratio,  $R_{pu}$  will be  $4R_{pd}$ . Clearly resistance  $R_{pu}$  value is  $R_{pu} = 4 R_s = 40 \text{K}\Omega$ . Meanwhile  $R_{pd}$  value is  $10 \text{K}\Omega$ .

Delay associated with inverter depends on ON and OFF condition of transistors.

Consider a pair of cascaded inverter, delay in this pair will be constant irrespective of sense of logic level transition. The overall delay of nmos inverter is  $\tau + 4\tau = 5\tau$ . Shown in below figure.

In general term delay through nmos inverter pair is given by  $T_d = (1 + Z_{pu}/Z_{pd}) \tau$

So single 4:1 inverter exhibits asymmetric delays, delay in turning on  $\tau$  (capacitor discharging condition) and delay in turning off is 4  $\tau$  (capacitor charging condition). Asymmetry becomes worse for inverter with 8:1 ratio.

For CMOS inverter, mos rules no longer applies, but we need to consider natural asymmetry of equal size pull up and pull down transistors.

Gate capacitance is double compare to nmos inverter since input is connected to both transistors and delay associated with pair of minimum size inverters is shown in below figure.

Asymmetry of resistance is eliminated by increasing the width of p- device channel by factor of two or three, but gate capacitance increases by the same factor.

### Driving large capacitive loads

- A large capacitive loads problem arises when a signal to be transmitted from On chip to Off chip destinations.

- Off chip capacitance is is generally higher than On chip  $\Box C_g$ . And it is denoted by  $C_L$ .

$$C_L \geq 10^4 \Box C_g$$

• A capacitance of this order to be driven through low resistance otherwise long delays will occur.

### **Cascaded Inverters as drivers**

- Inverters to drive large capacitive loads resistance associated with pull up and pull down transistors to be low.

- Low resistance values of  $Z_{pu}$  and  $Z_{pd}$  implies low L:W ratio or channel width must be made wider to reduce channel resistance but consequently inverter occupies large area.

- Gate area LxW is more significant and large capacitance present at input which slows down rate of change of voltage at input.

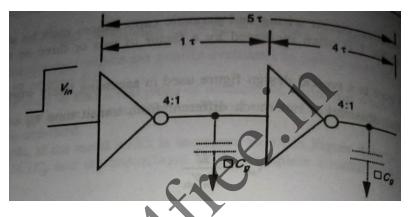

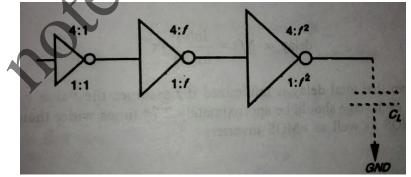

- Remedy to use N cascade inverter is by maintaining L to a minimum feature size and width of each successive stage is increased by factor f as shown in below figure.

- With increase in width factor increases capacitive load at input side and area occupied by the inverter also increases.

- The rate of width increase influence on number of stages to be cascaded to drive particular  $C_L$  value.

- Total delay associated with nmos pair is 5  $\tau$  and cmos pair is 7  $\tau$ .

Let  $y = {C_L / \Box C_g} = f^N$ , f and N are interdependent.

To determine value of f to minimize overall delay for given y  $\ln(y) = N \, \ln(f)$

N=

$$\frac{\ln(y)}{\ln(f)}$$

For N even, total delay =  $\frac{N}{2}5 f \tau = 2.5 f \tau$  (nmos) or

=  $\frac{N}{2}7 f \tau = 3.5 f \tau$  (cmos)

In all cases,  $\operatorname{delay} \dot{\alpha} \operatorname{N} f \tau = \frac{\ln(y)}{\ln(f)} f \tau$

• Total delay is minimized If *f* assumes the value e. i.e: each stage is approximately 2.7 times wider than its predecessor and it is applicable for both cmos and nmos inverters.

Thus assuming f = e, we have

Number of stages N = ln(y)

And overall delay  $t_d$

N even:  $t_d = 2.5 \text{ N } \tau \text{ (NMOS)}$  or  $t_d = 3.5 \text{ N } \tau \text{ (CMOS)}$ N odd:  $t_d = [2.5 \text{ (N-1)+1}] e \tau \text{ (NMOS)}$  or  $t_d = [3.5 \text{ (N-1)+1}] e \tau \text{ (CMOS)}$ For  $\Delta \text{Vin}$  which indicates logic 0 to 1 transistion of Vin.  $t_d = [2.5 \text{ (N-1)+4}] e \tau \text{ (NMOS)}$  or  $t_d = [3.5 \text{ (N-1)+5}] e \tau \text{ (CMOS)}$ For  $\Delta \text{Vin}$  which indicates logic 1 to 0 transistion of Vin.

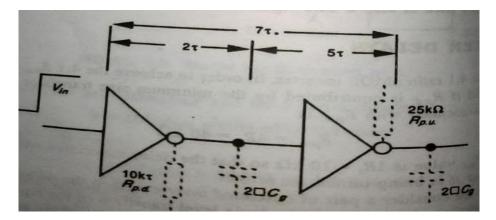

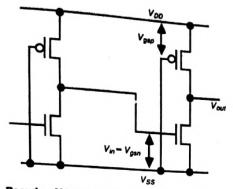

### Super buffers

• Asymmetry of conventional inverter gives rise to significant delay problems when used to drive large capacitive loads.

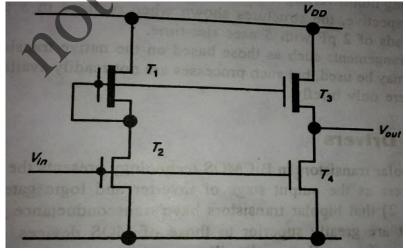

Common approach used in nmos inverter is to use super buffers an inverting type nmos super buffer is shown in figure.

• Consider input Vin = 1, the inverter formed by T1 and T2 is turned On and thus gate of T3 is pulled down to zero volts with small delay. So T3 is in cut off and T4 is turned On and output is pulled down.

- When Vin = 0, gate of T3 is allowed to rise to Vdd. Thus T4 turned Off, T3 is made to conduct with Vdd on its gate. The voltage applied to gate is twice the average voltage of conventional nmos inverter.

- Doubling effective Vgs will increase current, thus reduces the delay in charging capacitor at output, so symmetry is achieved.

- The Non-inverting type nmos inverter is shown in below figure.

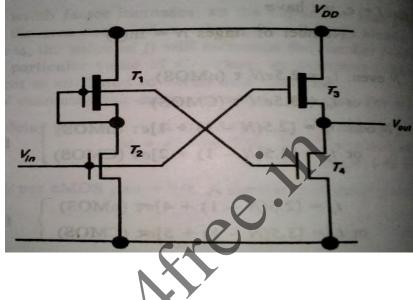

### **BICMOS Inverter**

- Bipolar transistor availability in Bicmos technology presents possibility of using bipolar transistors as drivers at the output stage of the inverter.

- Transconductance and current/area characteristics are superior than MOS devices. so it has high current driving capability.

- Bipolar transistor has exponential dependence of output current on base emitter voltage which means transistor can operate with small input voltage swing compared to MOS transistors and switches large current.

- So the bipolar transistors have better switching performance results in small input voltage swing and switch large current.

- Switching performance of transistor driving capacitive load can be seen from simple model.

- The time required to change output voltage Vout by an amount equal to input voltage is given by

$$\Delta t = \frac{C_L}{g_m}$$

Where  $g_m$  is trans conductance of bipolar transistor. As  $g_m$  increases  $\Delta t$  decreases.

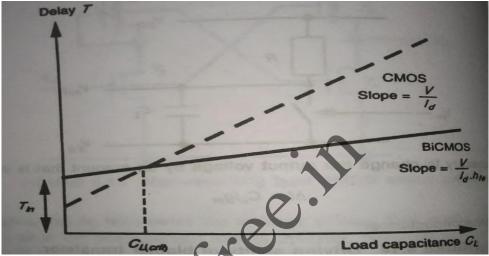

- Bipolar transistor delay has 2 main components Tin and  $T_L$ .

- Tin is the initial time required to charge the B-E junction of the transistor. It is time taken to charge the input gate capacitance.

- $T_L$  is time taken to charge the output load capacitance  $C_L$ . This value is less for bipolar by factor of  $h_{fe}$ .

- As BJT has higher Tin,  $T_L$  is small and because of this faster charging takes place and helps in reducing the delay.

- Combined effect of Tin &  $T_L$  is in graph. There is  $C_L$  critical load capacitance below which BICMOS driver is shown than CMOS driver.

- Delay of BICMOS is described by  $T = Tin + (V/I_d)(1/h_{fe})C_L$ .

- Delay for BICMOS inverter is reduced by a factor of *h<sub>fe</sub>* when compared with CMOS inverter.

# Module 3

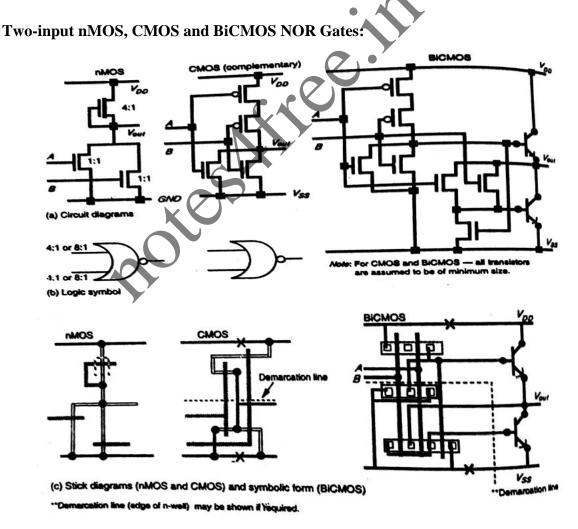

# **Scaling of MOS Circuits**

- High density chips in VLSI technology requires packing density of MOSFETS used is high and also the size of the transistors to be as small as possible. This reduction of size i.e. the dimension of MOSFET is referred as 'scaling'.

- It is expected that characteristics of the transistors will change with scaling and physical limitations will restrict the extent of scaling.

- Microelectronic technology is characterized in terms of indicators or figures of merit. The common figure of merits are

- Minimum feature size

- o Number of gates on one chip

- Power dissipation

- Maximum operational frequency

- o Die size

- Production cost

- The figure of merits can be improved by shrinking the dimensions of transistors, interconnections and the separation between features, adjusting doping levels and supply voltages.

- There are 2 types of size reduction/scaling strategies/ scaling models

- 1. Full scaling or constant-field scaling.

- 2. Constant-voltage scaling.

- Recently combined voltage and dimension model is presented. It is also called as 'Lateral scaling'

- Two scaling factors  $1/\alpha$  and  $1/\beta$  are used.

- $1/\beta$  is chosen as the scaling factor for supply voltage V<sub>DD</sub> and gate oxide thickness D

- $1/\alpha$  is used as scaling factor for other linear dimensions

- Scaling theory indicates that the characteristics of MOS devices can be maintained and the basic operational characteristics have to be preserved if the parameters of a device are scaled in accordance to a given criteria.

Constant field scaling: scaled device is obtained by applying dimension less factor to

- All dimensions

- Device voltages

- Concentration densities

## Scaling factors for device parameters:

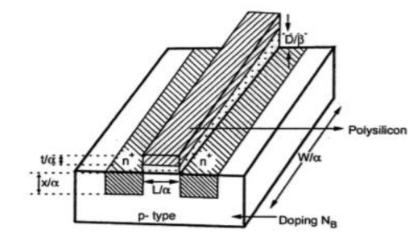

The device dimensions are shown in Fig. 3.1

Fig. 3.1 scaled nMOS transistor

1. Gate Area Ag

$1/\alpha$ .

$$A_g = L W$$

L and W defines channel length and width respectively. They are scaled by factor

Thus  $A_g$  is scaled by  $1/\alpha^2$

2. Gate Capacitance per Unit Area  $C_o$  or  $C_{ox}$

$C_0 \neq \frac{\sqrt{6}X}{D}$

$\mathcal{E}_{ox}$  is the permittivity of gate oxide and D is the thickness of gate oxide (thinox). Thus C<sub>o</sub> is scaled by  $\frac{1}{1/\beta} = \beta$

- 3. Gate Capacitance  $C_g$ Gate capacitance is given by,  $C_g = C_o L W$ Thus  $C_g$  is scaled by  $\beta * 1/\alpha^2 = \beta/\alpha^2$

- 4. Parasitic Capacitance  $C_x$

C<sub>x</sub>is proportional to A<sub>x</sub>/d

Where d depletion width around source or drain, it is scaled by  $1/\alpha$ . A<sub>x</sub> is area of depletion region around source and drain, it is scaled by  $1/\alpha^2$

Thus C<sub>x</sub> is scaled by  $(1/\alpha^2)/(1/\alpha) = 1/\alpha$

# 5. Carrier Density in channel $Q_{on}$

Qonis the average charge per unit area in the channel in the 'on' state.

$Q_{on} {=} C_o V_{gs}$  [C\_o is scaled by  $\beta \,$  and  $V_{gs} {is}$  scaled by  $1/\beta]$

Thus Q<sub>on</sub> is scaled by  $\beta * 1/\beta = 1$

6. Channel Resistance Ron

$$R_{\rm on} = \frac{L}{W} * 1/Q_{\rm on}\mu$$

L is scaled by  $1/\alpha$ , W is scaled by  $1/\alpha$ , Q<sub>on</sub>is scaled as 1,  $\mu$  is carrier mobility in the channel and is a constant.

Thus  $R_{on}$  is scaled by  $(1/\alpha)/(1/\alpha)*1/1=1$

7. Gate Delay  $T_d$

$$\begin{split} T_d \text{is proportional to } R_{on}. \ C_g \\ R_{on} \ \text{is scaled to } 1 \ \text{and } C_g \ \text{is scaled by } \beta/\alpha^2 \\ \text{Thus } T_d \ \text{is scaled to } 1^*\beta/\alpha^2 = \beta/\alpha^2 \end{split}$$

8. Maximum Operating Frequency  $f_o$

$$\begin{split} f_o &= W/L * (\mu C_o V_{DD})/C_g \\ \text{orf}_o \text{is inversely proportional to } T_d \\ \text{Thus } f_o \text{is scaled as } 1/(\beta/\alpha^2) &= \alpha^2/\beta \end{split}$$

9. Saturation Current Idss

1

$$U_{dss} = \frac{C_o \mu}{2} * \frac{W}{L} * (V_{gs} - V_t)^2$$

$C_o$  is scaled by  $\beta$ ,  $\mu$  and 2 are constants, W and L is scaled by  $1/\alpha$ ,  $V_{gs}$  and  $V_t$  both voltages are scaled by  $1/\beta$ . Thus  $I_{dss}$  is scaled by  $\beta^*(1/\beta)^2 = 1/\beta$

10. Current Density J

A is the cross sectional area of channel in 'on' state and is scaled by  $1/\alpha^2$  and  $I_{dss}$  is scaled by  $1/\beta$

Thus J is scaled by  $(1/\beta)/(1/\alpha^2) = \alpha^2/\beta$

11. Switching Energy per gate  $E_g$

$$E_g = \frac{1}{2} C_g V_{DD}^2$$

$C_g$  is scaled by  $\beta/\alpha^2$  and  $V_{DD}$  voltage is scaled by  $1/\beta$ . ThusE<sub>g</sub> is scaled by  $(\beta/\alpha^2)^*(1/\beta)^2 = 1/\alpha^2\beta$

12. Power Dissipation Per Gate Pg

$\begin{array}{l} P_g \text{ comprises 2 components, i.e., } P_g = P_{gs} + P_{gd} \\ P_{gs} \text{is the static component, given by } P_{gs} = (V_{DD})^2 / R_{on} \\ P_{gd} \text{is the dynamic component given by } P_{gd} = E_g * f_o \\ V_{DD} \text{is scaled by } 1/\beta, R_{on} \text{is scaled by 1} \\ E_g \text{ is scaled by } 1/\alpha^2 \beta, f_o \text{is scaled by } \alpha^2 / \beta \\ \text{Thus } P_{gs} \text{and } P_{gd} \text{ both are scaled by } (1/\beta)^2 \end{array}$

Thus  $P_g$  is scaled by  $1/\beta^2$

Power Dissipation Per Unit Area P<sub>a</sub>

P<sub>a</sub>is defined as scaled by

$$P_{a} = \frac{P_{s}}{A_{s}} = \frac{\left(\frac{1}{\beta^{2}}\right)}{\left(\frac{1}{\alpha^{2}}\right)} = \frac{\alpha^{2}}{\beta^{2}}$$

14. Power-Speed Product  $P_T$

$P_T = P_g * T_d$

$P_g$  is scaled by  $1/\beta^2$  and  $T_d$  is scaled by  $\beta/\alpha^2$

Thus P<sub>T</sub> is scaled by  $(1/\beta^2)^*(\beta/\alpha^2) = 1/\alpha^2\beta$

Summary of Scaling effects of all the 3 models is given in the table below

| Parameters                                              |                           | Combined V and D   | Constant E       | Constant V     |

|---------------------------------------------------------|---------------------------|--------------------|------------------|----------------|

| V <sub>DD</sub>                                         | Supply voltage            | 1/β                | 1/α              | 1              |